SawabyPlus

Newbie level 3

- Joined

- Oct 16, 2010

- Messages

- 3

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

- 1,303

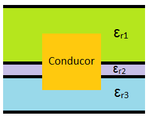

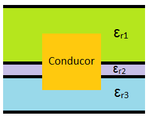

I am modeling transmission lines on ADS. Conductors in the technology I am using (CMOS) intrude into two or more dielectric layers similar to the sketch below. ADS 2011.01 does not allow conductor thickness to be equal to or larger than layer thickness. Does anyone know some workaround?

I thought of a couple of things, would the solution be valid if I use vias to draw conductor lines? or, is there a way to calculate the average permittivity of the layers that this conductor pass through? (there are some other layers for other conductors)

I thought of a couple of things, would the solution be valid if I use vias to draw conductor lines? or, is there a way to calculate the average permittivity of the layers that this conductor pass through? (there are some other layers for other conductors)