Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

Thank you for the document but still I don't know how to determine the sizing of the transistors

I tried to design one it operates only when the input voltage is high

Part 3 of the above linked document gives you optimization hints for the W/L ratios.

The necessary W/L ratios essentially depend on the process used, its p/n mobility ratio, and your priority either for speed, ICMR, or sensitivity.

For more help you should unveil this info, and the design schematic you've used so far.

Low power and speed are two opposing trends - you have to decide on a compromise.My priority is for power and speed

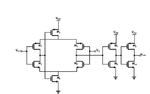

Without mentioning your process, and without your W/L ratios, it doesn't make much sense.I attached the same schematic I have used View attachment 116474

Low power and speed are two opposing trends - you have to decide on a compromise.

Without mentioning your process, and without your W/L ratios, it doesn't make much sense.

Low Power is my first

The process is UMC 0.13 and I am using minimum sizing for all transistors (3.3 transistors, W/L=160n/340n)

I don't have the UMC 0.13 models, so I tried with 0.18µm models. I think you could use the W/L ratios, perhaps scale them down a bit. But don't use min. size transistors (if you don't need max. speed).

View attachment 116492

Note:

I've used just one additional inverter, guess that's enough. In this case, the pos. and neg. inputs have to be swapped (relating to Vout1).

The ICMR is only about VDD/2 ± 250mV .

I think you could start from this schematic.

... when I increase the supply it doesn't work properly.

In this case decreasing the W/L ratios of M3 & M4 in proportion to the "inner" transistors may help:

View attachment 116515

Note:

Good luck!

- I've scaled down the W/L ratios by a factor of 2 - these should be fine for your 0.13µm process, I hope.

- Now a 2nd inverter stage is needed.

- The ICMR is shown in the image.

- As you know, I've used 0.18µm models. The circuit might not work with your models.

Try to adjust the width ratio W(PMOS)/W(NMOS) to the low-field mobility ratio U0(NMOS)/U0(PMOS) of your process. It's probably close to 3 . You can find the U0 values in your models.

Why the input has to be greater than half of the supply?