NadaElfamy

Newbie

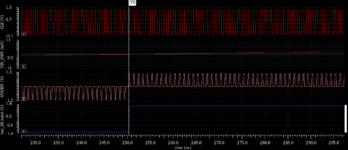

I have two questions, now i'am designing a comparator followed by Buffer then SR latch for ADC, and i wanna test the offset of this comparator, so i put a PWL (ramp input) in one of the inputs and a DC volt (VREF) in the other input,

First question: Should i check the output of the comparator or output from the SR latch (as the output of the comparator will suffer from the delay of the buffer and SR latch, so if i checked the output of SR latch this delay will be considered an extra offset).

Second question: And if it is not a difference, how should i calculate the offset from each one (comparator output or SR latch output).

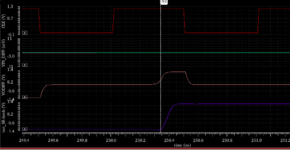

Comment: the second figure (capture2) is to clarify the delay of the comparator output and the SR latch output

First question: Should i check the output of the comparator or output from the SR latch (as the output of the comparator will suffer from the delay of the buffer and SR latch, so if i checked the output of SR latch this delay will be considered an extra offset).

Second question: And if it is not a difference, how should i calculate the offset from each one (comparator output or SR latch output).

Comment: the second figure (capture2) is to clarify the delay of the comparator output and the SR latch output