cmos_ajay

Full Member level 2

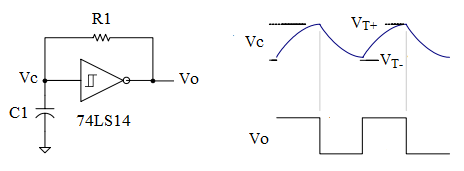

Hello, I need a suitable comparator architecture in standard CMOS process for a relaxation oscillator. This oscillator has 2 comparators and 2 caps. Frequency = 20 Meg and VCC supply = 5V.

Basically a high speed low propagation delay comparator circuit is needed to get good linearity. Can some suggest papers that might prove helpful ?

Basically a high speed low propagation delay comparator circuit is needed to get good linearity. Can some suggest papers that might prove helpful ?