aruna1

Member level 1

Hi all,

I'm reading on CMOS and came across following fact

I was searching through the internet but couldn't find any information explain how low threshold voltage is fast but consume more power and how high threshold voltage is slow but consumes low power.

All the documents I came across simply states "lvt is for fast, and hvt is for slow,low power"

So can somebody please explain how FET with low threshold voltage has higher speed and higher leakage current while FET with high threshold will be slow but low on power?

Thank you very much.

I'm reading on CMOS and came across following fact

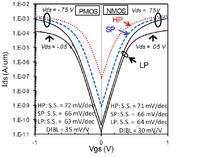

CMOS with low threshold voltage (lvt) is used in high-speed (time critical) designs but they have higher leakage power consumption

CMOS with high threshold voltage (hvt) is used in low-speed (not time critical) designs but they have lower leakage power consumption

I was searching through the internet but couldn't find any information explain how low threshold voltage is fast but consume more power and how high threshold voltage is slow but consumes low power.

All the documents I came across simply states "lvt is for fast, and hvt is for slow,low power"

So can somebody please explain how FET with low threshold voltage has higher speed and higher leakage current while FET with high threshold will be slow but low on power?

Thank you very much.