latvian

Newbie level 3

Hello everyone,

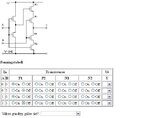

I have this question in my homework that I am having problem solving it. The question is a CMOS network of gates that I must give the truth table of it and to choose the type of the network.

The choices for the y are: 0, 1, z

The choices for the type of network is: tri-state inverter, tri-state buffer, AND network, OR network, NAND, NOR, XOR, XNOR.

The question is attached with this question as a screen shot image...

Please help!

Thanks in advance

I have this question in my homework that I am having problem solving it. The question is a CMOS network of gates that I must give the truth table of it and to choose the type of the network.

The choices for the y are: 0, 1, z

The choices for the type of network is: tri-state inverter, tri-state buffer, AND network, OR network, NAND, NOR, XOR, XNOR.

The question is attached with this question as a screen shot image...

Please help!

Thanks in advance