coshy

Member level 4

Dear All,

I've been trying to study a Clock Gating Insertion. So I've find good reference https://stackoverflow.com/questions/24977925/how-to-use-clock-gating-in-rtl/25003974#25003974

And, I've applied to my example code as the below

and I Synthesis with SDC as below

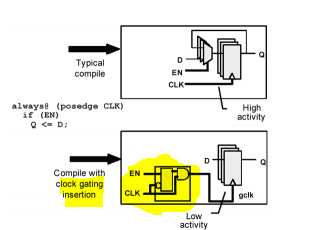

I expect the synthesized gate netlist is as the below

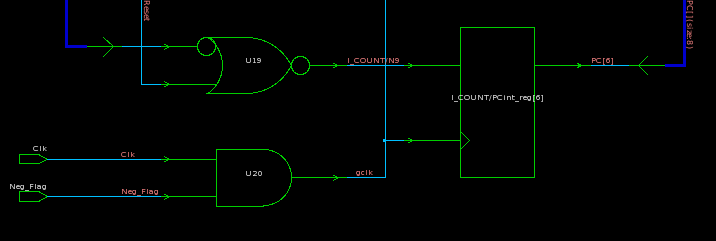

But netlist compiled as the below

Even the Timing report also didn't show me any Clock-Gating relative Timing Report.

How To implement a Clock Gating methodology into gate netlist and got the Clock Gating Report in DC ? Does ICG cell inserting mean that using target library ICG cell?

I've been trying to study a Clock Gating Insertion. So I've find good reference https://stackoverflow.com/questions/24977925/how-to-use-clock-gating-in-rtl/25003974#25003974

And, I've applied to my example code as the below

Code:

`define RESET_STATE 3'b000

`define FETCH_INSTR 3'b001

`define READ_OPS 3'b010

`define EXECUTE 3'b011

`define WRITEBACK 3'b100

module TOP(Clk, Reset, Crnt_Instrn, Neg_Flag, PC);

input Clk;

input Reset;

input [31:0] Crnt_Instrn; // Current Executing Inst

input Neg_Flag; // Flags from ALU or Stack

output [7:0] PC; // Program Count

wire Ld_Brnch_Addr;

wire gclk;

omsp_clock_gate u_omsp_clock_gate (

// OUTPUTs

.gclk ( gclk ), // Gated clock

// INPUTs

.clk ( Clk ), // Clock

.enable ( Neg_Flag ), // Clock enable

.scan_enable ( 1'b0) // Scan enable (active during scan shifting)

);

COUNT I_COUNT (

.Reset(Reset),

.Clk(gclk),

// .Clk(Clk),

.Imm_Addr(Crnt_Instrn[7:0]),

.PC(PC)

);

endmodule

module COUNT(Reset, Clk, Imm_Addr, PC);

input Reset, Clk ; // Reset for the PC

input [7:0] Imm_Addr; // Immediate Addr for Jmp/Call

output [7:0] PC; // Addr of instruction to be fetched in

// the next Fetch Cycle

reg [7:0] PCint;

always @(posedge Clk) begin

if (Reset == 1'b1) begin

PCint <= 8'b00000000;

end else begin

PCint <= Imm_Addr;

end

end

assign PC = PCint;

endmodule

module omsp_clock_gate (

// OUTPUTs

gclk, // Gated clock

// INPUTs

clk, // Clock

enable, // Clock enable

scan_enable // Scan enable (active during scan shifting)

);

// OUTPUTs

//=========

output wire gclk; // Gated clock

// INPUTs

//=========

input clk; // Clock

input enable; // Clock enable

input scan_enable; // Scan enable (active during scan shifting)

///////////////////////////////////////////////////////////////////////////////////

wire enable_in = (enable | scan_enable);

assign gclk = enable_in & clk;

endmodule // omsp_clock_gateand I Synthesis with SDC as below

Code:

reset_design

remove_design -all

alias

check_library

read_file -format verilog ./rtl/TOP.v

current_design TOP

link

current_design TOP

## Create clock object and set uncertainty

create_clock -period 2 [get_ports Clk]

set_clock_uncertainty 0.2 [get_clocks Clk]

## Set constraints on input ports

suppress_message UID-401

set_input_delay 0.1 -max -clock Clk [remove_from_collection [all_inputs] [get_ports Clk]]

set_input_delay 1.2 -max -clock Clk [get_ports Neg_Flag]

## Set constraints on output ports

set_output_delay 1 -max -clock Clk [all_outputs]

compile_ultra

report_constraint -all > ./report_constraint_all.rpt

report_timing -max_paths 100 > ./report_timing.rpt

report_area > ./report_area.rptI expect the synthesized gate netlist is as the below

But netlist compiled as the below

Even the Timing report also didn't show me any Clock-Gating relative Timing Report.

How To implement a Clock Gating methodology into gate netlist and got the Clock Gating Report in DC ? Does ICG cell inserting mean that using target library ICG cell?

Last edited: