nanock

Member level 1

Hi,

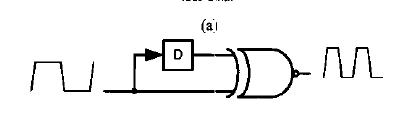

I have two clock outputs, one with 60% duty cycle and the other one with 40% duty cycle. I want to convert one of these, no matter which one will be, to 50% duty cycle.

Is it possible?

How can I convert a 60% or 40% duty cycle to 50% ?

thanks

I have two clock outputs, one with 60% duty cycle and the other one with 40% duty cycle. I want to convert one of these, no matter which one will be, to 50% duty cycle.

Is it possible?

How can I convert a 60% or 40% duty cycle to 50% ?

thanks