kaixi

Newbie level 5

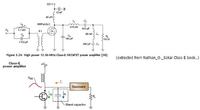

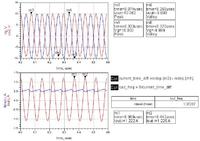

Hi does anyone has idea on designing a Class E power amplifier operating at 13.56Mhz?

The series LC should match the input frequency.

How about the value of L at drain and shunt C value?

For single ended design, the component should only include series LC, L at drain and shunt C across drain source right?

Resonating component will be C at drain source and series LC?

or only the series LC?

The series LC should match the input frequency.

How about the value of L at drain and shunt C value?

For single ended design, the component should only include series LC, L at drain and shunt C across drain source right?

Resonating component will be C at drain source and series LC?

or only the series LC?