AMSA84

Advanced Member level 2

- Joined

- Aug 24, 2010

- Messages

- 577

- Helped

- 8

- Reputation

- 16

- Reaction score

- 8

- Trophy points

- 1,298

- Location

- Iberian Peninsula

- Activity points

- 6,178

Hi guys,

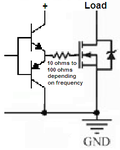

I'd like to know if someone can help me simulate a Class B amplifier? From what I have seen, it is like the inverter, but in place of the PMOS (in the inverter) it has the NMOS and in place of NMOS (in the inverter) has the PMOS.

I tried to simulate but the results are not the same as in some literature that I have read.

Regards.

I'd like to know if someone can help me simulate a Class B amplifier? From what I have seen, it is like the inverter, but in place of the PMOS (in the inverter) it has the NMOS and in place of NMOS (in the inverter) has the PMOS.

I tried to simulate but the results are not the same as in some literature that I have read.

Regards.