ASIC_int

Advanced Member level 4

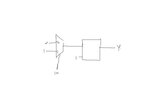

1) Y= '0'.

2) The netlist should not be a 2:1 mux. It is because casex is synthesizable. So it will try to produce a gate level structute where even if in='X' , the output should be 1'b0. Si the tool will try to look for gate in the library that can realize such a gate level netlist. So Y= '0' when in= x.

lostinxlation

lostinxlation

You still did not reply the following:

"A casex treats X as don't cares if they are in either the case expression or the case item".

What does it mean to state that casex treats case expression as don't care?

2) The netlist should not be a 2:1 mux. It is because casex is synthesizable. So it will try to produce a gate level structute where even if in='X' , the output should be 1'b0. Si the tool will try to look for gate in the library that can realize such a gate level netlist. So Y= '0' when in= x.

lostinxlation

lostinxlation

You still did not reply the following:

"A casex treats X as don't cares if they are in either the case expression or the case item".

What does it mean to state that casex treats case expression as don't care?