muyil

Newbie level 4

Hi Everyone,

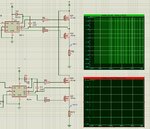

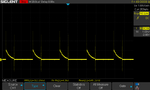

I have been testing my inverter design recently. I tried to apply 150V to h-bridge as a bus voltage but it started to pull a lot of current and the 150V dropped down to 50 volts. The circuit doesn't pull much current below 50 volts. Why could this be happening? I am using ir2110 driver IC and didn't apply any dead time. Could this be the problem? If so, how can I solve that? It works well with the simulation as well.

Regards

I have been testing my inverter design recently. I tried to apply 150V to h-bridge as a bus voltage but it started to pull a lot of current and the 150V dropped down to 50 volts. The circuit doesn't pull much current below 50 volts. Why could this be happening? I am using ir2110 driver IC and didn't apply any dead time. Could this be the problem? If so, how can I solve that? It works well with the simulation as well.

Regards