saifaljanahi

Newbie level 6

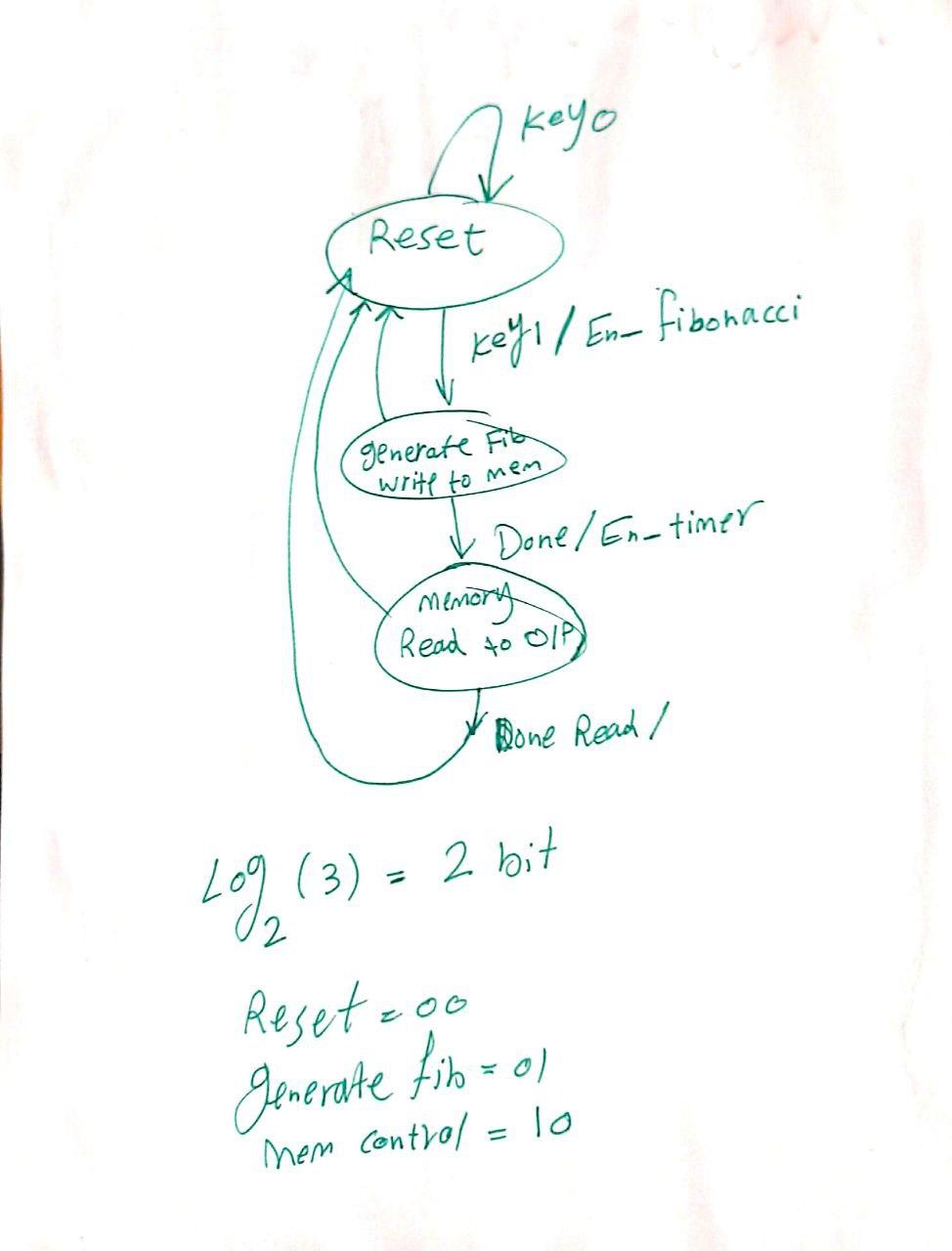

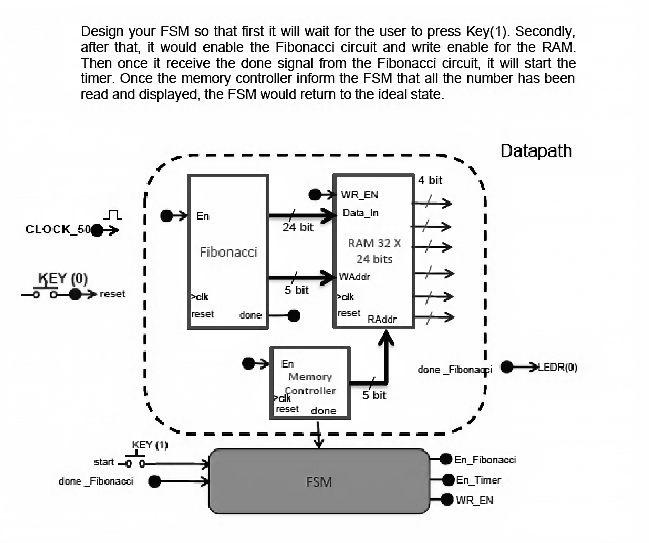

Hello all, I want to show you the FSM diagram that implements the block diagram shown below, this is my effort to the course project, I have the code if anyone want to check it.

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

Thanks,The problem description doesn't seem to match what you drew as your FSM.

There isn't anything mentioned in the text for transitioning from the 2nd state to the Reset state. Also, there are two transitions from the 3rd state back to the first state. You also don't have any transition that loops in both the 2nd and 3rd states to account for the "receive the done signal" and the "all number has been read and displayed" respectively.

Thanks, I've modified it according to your recommendation and according to the text.ideal state? I think you mean an idle state.

Yes you need to follow what the design requirements are, which is the problem description your instructor gave you. Right now the FSM sequence of states doesn't do anything close to what the sequence describe by the problem text.

The block diagram shows you what the instructor wants your signal names to be that go between FSM and the other blocks.

Also I didn't look at the block diagram all that closely, so didn't realize you were cycling in state Reset with Key0, Key0 should be a FSM reset signal forcing the FSM to the IDLE state.

Also you need to debounce and synchronize any switch input like these Key0/1 inputs to the FSM clock.