mfhanif

Junior Member level 2

DRC error

Hi,

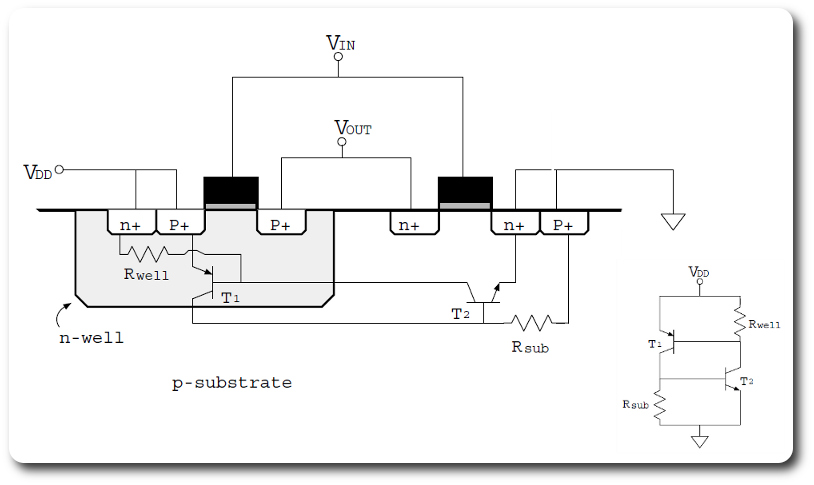

I have auto generated layout from the schematic; while running the DRC i am getting "Nmos to pwell contact max 30um"..... can anybody explain the meaning of this error ....

thanks

Hi,

I have auto generated layout from the schematic; while running the DRC i am getting "Nmos to pwell contact max 30um"..... can anybody explain the meaning of this error ....

thanks