ianrox

Newbie level 5

Hi

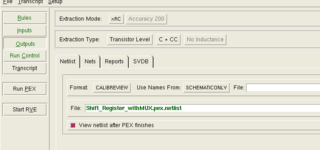

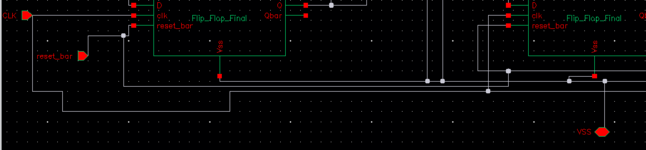

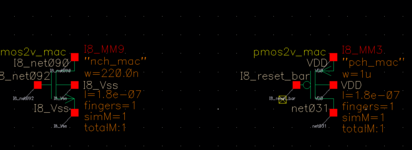

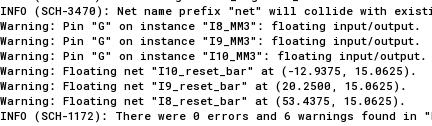

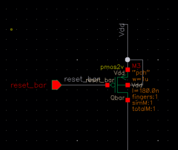

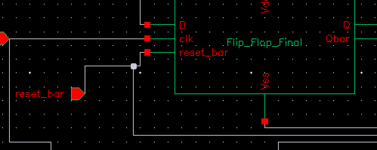

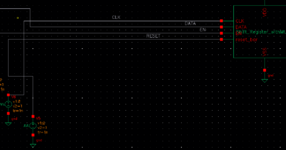

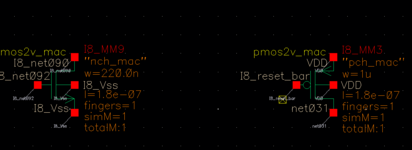

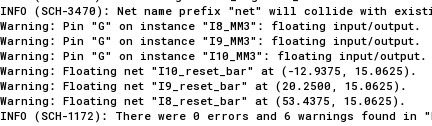

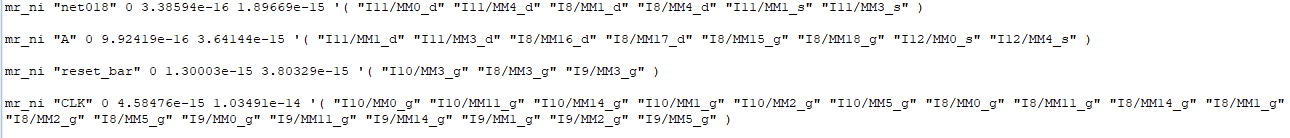

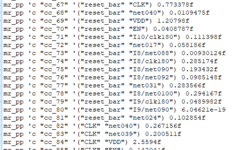

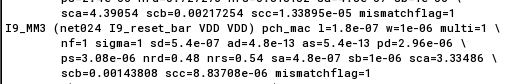

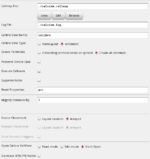

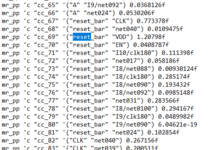

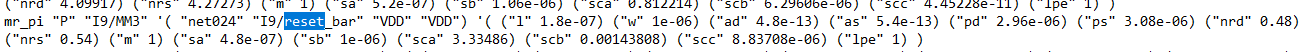

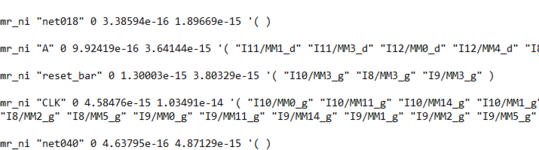

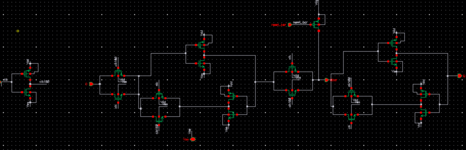

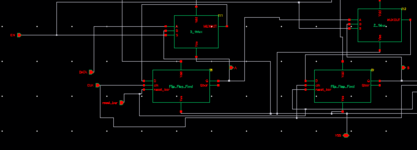

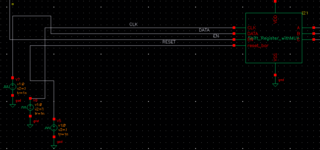

I am facing a strange issue on pex extraction. I am making a simple device and created the layout. LVS is clean. When I do a transistor level R+C+CC extraction, there is no warning and the calibre extracted simulation works as expected. However to speed simulations, when I try a C+CC extraction, there are 3 floating gate warnings and the calibre extracted simulation fails. I tried finding a cause but to no success. Any help would be greatly appreciated.

I am facing a strange issue on pex extraction. I am making a simple device and created the layout. LVS is clean. When I do a transistor level R+C+CC extraction, there is no warning and the calibre extracted simulation works as expected. However to speed simulations, when I try a C+CC extraction, there are 3 floating gate warnings and the calibre extracted simulation fails. I tried finding a cause but to no success. Any help would be greatly appreciated.