Khalid_Eissa

Newbie

Hi,

I am trying to perform stability analysis on an LDO circuit, everything was great and the results were close to expectations when I was using ideal VDD and GND.

When I added VDD bond-wire (L and R) and also GND bond-wire, the results became very weird: the DC gain has significantly dropped (like 40dB) and the loop phase changed from starting at 180 degree to starting at 0. also I got very wierd high frequency behavior.

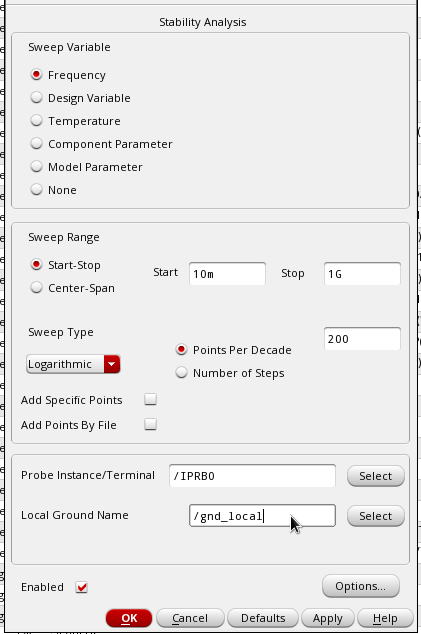

When I specified the local grnd name as shown in the following pic to be the internal gnd (before gnd bond-wire and not ideal gnd), the results went back to normal and everything is now OK (same results as before I add the bond-wires to VDD and GND except for some minor differences at very high frequencies, which were expected because of the addition of bond-wires)

So my questions is the following: which solution is the correct solution? before specifying Local Ground Name or after specifying it? and why?

I tried searching online for any material describing how cadence solve and get the loop transfer function with and without specifying local ground name, but I have found nothing unfortunately. Can anyone help please?

Thanks a lot

I am trying to perform stability analysis on an LDO circuit, everything was great and the results were close to expectations when I was using ideal VDD and GND.

When I added VDD bond-wire (L and R) and also GND bond-wire, the results became very weird: the DC gain has significantly dropped (like 40dB) and the loop phase changed from starting at 180 degree to starting at 0. also I got very wierd high frequency behavior.

When I specified the local grnd name as shown in the following pic to be the internal gnd (before gnd bond-wire and not ideal gnd), the results went back to normal and everything is now OK (same results as before I add the bond-wires to VDD and GND except for some minor differences at very high frequencies, which were expected because of the addition of bond-wires)

So my questions is the following: which solution is the correct solution? before specifying Local Ground Name or after specifying it? and why?

I tried searching online for any material describing how cadence solve and get the loop transfer function with and without specifying local ground name, but I have found nothing unfortunately. Can anyone help please?

Thanks a lot