soumen21

Member level 5

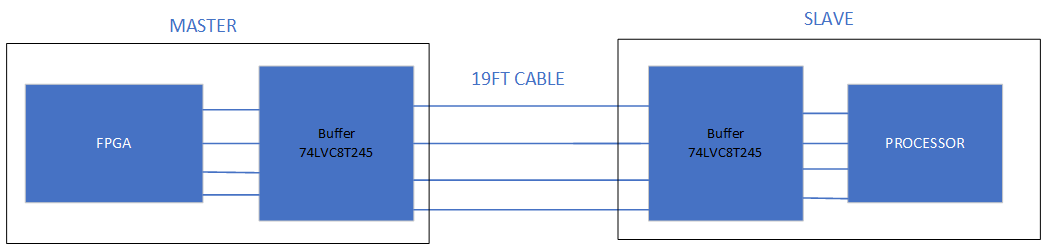

I have a Master and a SPI slave device. On the master end I have FPGA and buffers and on slave side buffers and Processor. Arrangement shown below

The above works fine for distance of the slave device from the controller up to 22 feet. The devices are placed on a carrier board. Processor on the slave is MC68HC705C9A (5V operated)

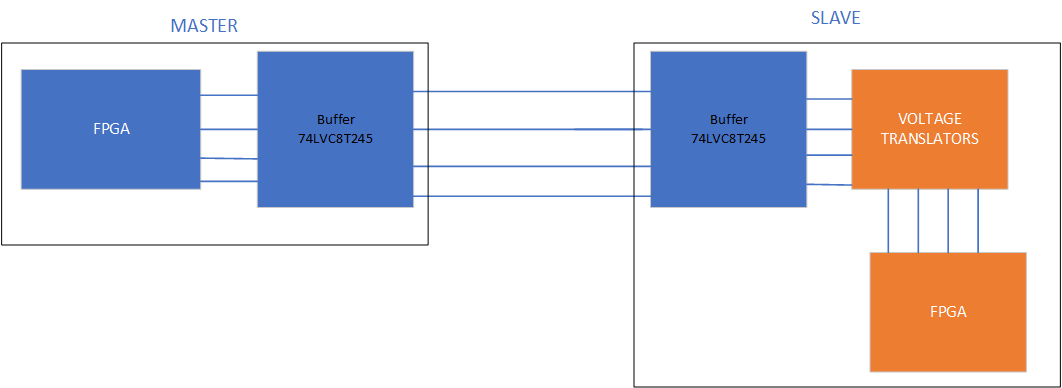

In the new arrangement (shown below), for a required change, the processor is replaced with SPARTAN 3 FPGA and level translators are used to make the signals compatible to 3.3V of the FPGA.

With the new arrangement with FPGA and voltage translators, the master sometime reports IO device communication error when the device is below 16ft from the MASTER.

And when the distance from the Master to slave is more than 16 feet, the the MASTER always reports IO device communication error.

What could be the probable issue?

Regards

Soumen

The above works fine for distance of the slave device from the controller up to 22 feet. The devices are placed on a carrier board. Processor on the slave is MC68HC705C9A (5V operated)

In the new arrangement (shown below), for a required change, the processor is replaced with SPARTAN 3 FPGA and level translators are used to make the signals compatible to 3.3V of the FPGA.

With the new arrangement with FPGA and voltage translators, the master sometime reports IO device communication error when the device is below 16ft from the MASTER.

And when the distance from the Master to slave is more than 16 feet, the the MASTER always reports IO device communication error.

What could be the probable issue?

Regards

Soumen