Junus2012

Advanced Member level 5

Hello,

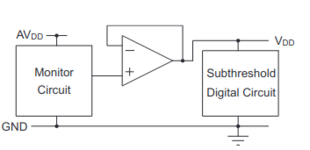

I am using the buffer like the picture shown below. The unity gain buffer amplifier is buffering the input voltage and use it as the supply voltage source for the coming digital cell.

It very known that for the digital cmos gates, the supply current and is proportional to the frequency of operation and the digital cells consumes the highest current in the transition region.

So what is happening here is that the buffered opamp need to supply this current otherwise the buffer output will drop.

What is possible solution to improve the current driving capability of the buffer ?

Do we need a low output opamp, or even OTA can serve in this purpose?

Thank you

Regards

I am using the buffer like the picture shown below. The unity gain buffer amplifier is buffering the input voltage and use it as the supply voltage source for the coming digital cell.

It very known that for the digital cmos gates, the supply current and is proportional to the frequency of operation and the digital cells consumes the highest current in the transition region.

So what is happening here is that the buffered opamp need to supply this current otherwise the buffer output will drop.

What is possible solution to improve the current driving capability of the buffer ?

Do we need a low output opamp, or even OTA can serve in this purpose?

Thank you

Regards