YoungEN

Newbie

Hi, there!

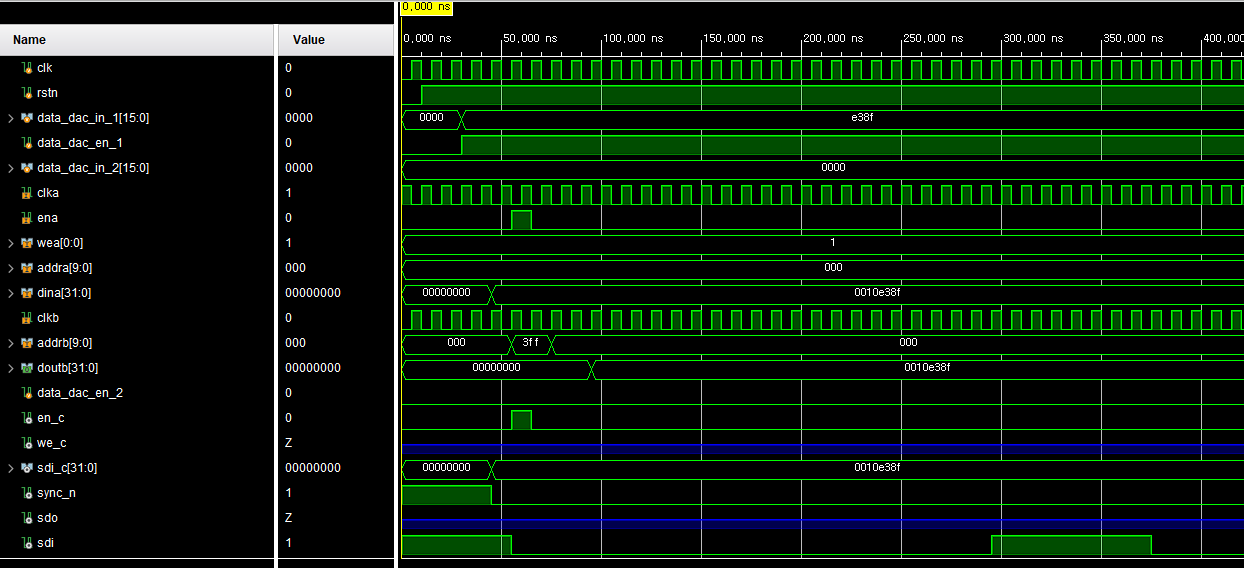

I recently trying to use BRAM as Simple DPRAM in Logic.

just send the 16bit data by register through AXI from Zynq, and received data store in BRAM and out through the my logic.

The thing is simulation is working properly... but in hardware isn't...

So I tried to write just register and out is properly worked...

How can I fix this errors.. Hope you guys give me a advise.. Thanks..

Here's my code below

module ad5764#(

parameter ADDR_WIDTH = 9,

parameter ADDR_DEPTH_DIV = 128,

parameter KHZ = 2500,

parameter default_val = 24'b00010100100000000000000,

parameter CONFIG = 5'b00010,

parameter MUX = 1,

parameter SEQ = 00,

parameter OTHER = 4'b1110

)(

input wire [15:0] data_dac_in_1, // regin

input wire [15:0] data_dac_in_2,//reg in

input wire [15:0] data_dac_in_3, //reg in

input wire [15:0] data_dac_in_4, // reg in

input wire data_dac_en_1, //reg in

input wire data_dac_en_2, //reg in

input wire data_dac_en_3, //reg in

input wire data_dac_en_4, // regin

input wire sdo,

input wire rstn,

input wire clk,

input wire [12:0] read_addrs,

output wire sdi,

output wire sclk,

output wire sync_n,

output wire ldac_n,

output wire interrupt,

input wire clkb, //bram clk

output wire [31:0] data_out, //read to bram

//tast pins

output wire [31:0] sdi_c,

// output wire [2:0] st,

//output wire [5:0] det,

//output wire [6:0] addr_a, addr_b,

output wire en_c,

//output wire we_c,

//output wire [5:0] det_1,

//output wire sclk_c,

output wire [6:0] addr_i

);

reg [15:0] i_data_dac_1, i_data_dac_2, i_data_dac_3, i_data_dac_4;

reg [2:0] STATE = 3'b110, IDLE = 3'b111, DAC1 = 3'b000, DAC2 = 3'b001, DAC3 = 3'b010, DAC4 = 3'b011;

reg [ADDR_WIDTH:0] dac_go, dac_out;

reg [ADDR_WIDTH:0] i_addrs;

reg [5:0] data_reg, data_reg_1, data_reg_2, data_reg_3, data_reg_4;

reg [15:0] i_dac1, i_dac2, i_dac3, i_dac4;

reg cs_n = 1;

reg done = 0;

reg [5:0] data_cnt, data_cnt_1, data_cnt_2, data_cnt_3, data_cnt_4;

wire [31:0] data_in;

wire [15:0] sdi_o;

reg [0:23] sdi_out;

wire sck_in;

reg [0:23] sdi_in;

reg [4:0] out_cnt;

reg sck_o = 0;

reg [5:0] done_cnt = 0;

wire [5:0] in_bram_addrs;

reg [2:0] sck_cnt;

reg [2:0] out_time_cnt;

reg ldac_in, ldac_go;

reg [5:0] ldac_cnt;

reg [0:23] dac_store;

reg we_d, en_d;

reg data_shift;

reg i_en, i_we;

reg [6:0] a_addrs, b_addrs, c_addrs, d_addrs, h_addrs;

reg config_go;

wire [0:23] config_data;

reg CS_ST, STAY = 1'b0, RUN = 1'b1;

reg [31:0] data_dac;

reg [31:0] i_dac_data;

reg [7:0] addr_cnt;

reg [9:0] i_r_addrs;

reg i_interrupt;

reg o_interrupt;

reg [12:0] interrupt_cnt;

reg done_en;

reg [7:0] config_in;

reg en_sh1, en_sh2;

wire en_sh_o;

reg [15:0] i_data_dac_in_1;

reg [15:0] i_data_dac_in_2;

reg [15:0] i_data_dac_in_3;

reg [15:0] i_data_dac_in_4;

reg data_go_1, data_go_2, data_go_3, data_go_4;

reg en_done;

assign sdi_o = data_in[15:0];

assign sclk = sck_o;

assign sync_n = cs_n;

assign ldac_n = ldac_in;

assign interrupt = o_interrupt;

assign sdi = sdi_in;

assign sdi_c = i_dac_data;

assign en_sh_o = (en_sh1 && ~en_sh2);

assign sdi_o = data_in[15:0];

assign sclk = sck_o;

assign sync_n = cs_n;

assign ldac_n = ldac_in;

assign interrupt = o_interrupt;

assign sdi = sdi_in;

// assign addr_i = i_r_addrs;

// assign sdi_c = sdi_out;

// assign st = STATE;

assign en_c = en_sh_o;

//assign we_c = i_we;

assign sdi_c = i_dac_data;

assign en_sh_o = (en_sh1 && ~en_sh2); //|| //(~en_sh1 && en_sh2));

always @(posedge sck_in or negedge rstn) begin

if(!rstn) begin

CS_ST <= RUN;

sck_cnt <= 0;

done <= 0;

end

else begin

case (CS_ST)

RUN : begin

done <= 0;

cs_n <= 0;

if(out_cnt == 23) begin

CS_ST <= STAY;

cs_n <= 1;

end

end

STAY : begin

done<=1;

cs_n <= 1;

sck_cnt <= sck_cnt + 1;

if (sck_cnt == 2) begin

CS_ST <= RUN;

sck_cnt <= 0;

done <= 1;

end

end

endcase

end

end

always @(posedge clk or negedge rstn) begin

if(!rstn) begin

i_en <= 0;

i_we <= 0;

i_addrs <= 0;

i_dac_data <= 0;

i_data_dac_in_1 <= 0;

i_data_dac_in_2 <= 0;

i_data_dac_in_3 <= 0;

i_data_dac_in_4 <= 0;

data_go_1 <= 0;

data_go_2 <= 0;

data_go_3 <= 0;

data_go_4 <= 0;

end

else begin

i_data_dac_in_1 <= data_dac_in_1;

i_data_dac_in_2 <= data_dac_in_2;

i_data_dac_in_3 <= data_dac_in_3;

i_data_dac_in_4 <= data_dac_in_4;

if(i_data_dac_in_1 != data_dac_in_1) begin

data_go_1 <= 1;

end

else if(i_data_dac_in_2 != data_dac_in_2) begin

data_go_2 <= 1;

end

else if(i_data_dac_in_3 != data_dac_in_3) begin

data_go_3 <= 1;

end

else if(i_data_dac_in_4 != data_dac_in_4) begin

data_go_4 <= 1;

end

else if(data_dac_en_1 && data_go_1) begin

i_dac_data <= {8'b0,CONFIG,3'b000,data_dac_in_1};

i_addrs <= a_addrs;

i_en <= 1;

if (en_done) begin

i_en <= 0;

data_go_1 <= 0;

end

end

else if(data_dac_en_2 && data_go_2) begin

// if(data_dac_en_2) begin

i_dac_data <= {8'b0,CONFIG,3'b001,data_dac_in_2};

i_we <= 1;

i_en <= 1;

i_addrs <= b_addrs + ADDR_DEPTH_DIV;

if (en_done) begin

i_en <= 0;

data_go_2 <= 0;

end

// end

end

else if(data_dac_en_3 && data_go_3) begin

//if(data_dac_en_3) begin

i_dac_data <= {8'b0,CONFIG,3'b010,data_dac_in_3};

i_we <= 1;

i_en <= 1;

i_addrs <= c_addrs + 2*ADDR_DEPTH_DIV;

if (en_done) begin

i_en <= 0;

data_go_3 <= 0;

end

end

else if(data_dac_en_4) begin

//if(data_dac_en_4) begin

i_dac_data <= {8'b0,CONFIG,3'b011,data_dac_in_4};

i_en <= ~i_en;

i_addrs <= d_addrs + 3*ADDR_DEPTH_DIV;

if (en_done) begin

i_en <= 0;

data_go_4 <= 0;

end

//end

end

end

end

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

en_sh1 <= 0;

en_sh2 <= 0;

en_done <= 0;

end

else begin

en_sh1 <= i_en;

en_sh2 <= en_sh1;

en_done <= 1;

if(!i_en) begin

en_done <= 0;

end

end

end

always @(negedge i_en or negedge rstn) begin

if (!rstn) begin

//i_addrs <= 0;

//h_addrs <= 0;

a_addrs <= 0;

b_addrs <= 0;

c_addrs <= 0;

d_addrs <= 0;

end

else begin

case (i_dac_data[18:16])

3'b000 : begin

a_addrs <= a_addrs +1;

end

3'b001 : begin

b_addrs <= b_addrs + 1;

end

3'b010 : begin

c_addrs <= c_addrs + 1;

end

3'b011 : begin

d_addrs <= d_addrs + 1;

end

endcase

end

end

dac_ram date_rx(

// Port A

.addra(i_addrs),

.clka(clk),

.dina(i_dac_data),

.ena(en_sh_o),

.wea(1'b1),

//Port B

.addrb(i_r_addrs),

.clkb(clk),

.doutb(data_in)

);

dac_ram data_o(

.addra(i_addrs),

.clka(clk),

.dina(i_dac_data),

.ena(en_sh_o),

.wea(1'b1),

//Port B

.addrb(read_addrs[10:0]),

.clkb(clkb),

.doutb(data_out)

);

endmodule

BRAM Trans

I couldn't write all the code by limit... but other side is working properly...

This is BRAM write side

I recently trying to use BRAM as Simple DPRAM in Logic.

just send the 16bit data by register through AXI from Zynq, and received data store in BRAM and out through the my logic.

The thing is simulation is working properly... but in hardware isn't...

So I tried to write just register and out is properly worked...

How can I fix this errors.. Hope you guys give me a advise.. Thanks..

Here's my code below

module ad5764#(

parameter ADDR_WIDTH = 9,

parameter ADDR_DEPTH_DIV = 128,

parameter KHZ = 2500,

parameter default_val = 24'b00010100100000000000000,

parameter CONFIG = 5'b00010,

parameter MUX = 1,

parameter SEQ = 00,

parameter OTHER = 4'b1110

)(

input wire [15:0] data_dac_in_1, // regin

input wire [15:0] data_dac_in_2,//reg in

input wire [15:0] data_dac_in_3, //reg in

input wire [15:0] data_dac_in_4, // reg in

input wire data_dac_en_1, //reg in

input wire data_dac_en_2, //reg in

input wire data_dac_en_3, //reg in

input wire data_dac_en_4, // regin

input wire sdo,

input wire rstn,

input wire clk,

input wire [12:0] read_addrs,

output wire sdi,

output wire sclk,

output wire sync_n,

output wire ldac_n,

output wire interrupt,

input wire clkb, //bram clk

output wire [31:0] data_out, //read to bram

//tast pins

output wire [31:0] sdi_c,

// output wire [2:0] st,

//output wire [5:0] det,

//output wire [6:0] addr_a, addr_b,

output wire en_c,

//output wire we_c,

//output wire [5:0] det_1,

//output wire sclk_c,

output wire [6:0] addr_i

);

reg [15:0] i_data_dac_1, i_data_dac_2, i_data_dac_3, i_data_dac_4;

reg [2:0] STATE = 3'b110, IDLE = 3'b111, DAC1 = 3'b000, DAC2 = 3'b001, DAC3 = 3'b010, DAC4 = 3'b011;

reg [ADDR_WIDTH:0] dac_go, dac_out;

reg [ADDR_WIDTH:0] i_addrs;

reg [5:0] data_reg, data_reg_1, data_reg_2, data_reg_3, data_reg_4;

reg [15:0] i_dac1, i_dac2, i_dac3, i_dac4;

reg cs_n = 1;

reg done = 0;

reg [5:0] data_cnt, data_cnt_1, data_cnt_2, data_cnt_3, data_cnt_4;

wire [31:0] data_in;

wire [15:0] sdi_o;

reg [0:23] sdi_out;

wire sck_in;

reg [0:23] sdi_in;

reg [4:0] out_cnt;

reg sck_o = 0;

reg [5:0] done_cnt = 0;

wire [5:0] in_bram_addrs;

reg [2:0] sck_cnt;

reg [2:0] out_time_cnt;

reg ldac_in, ldac_go;

reg [5:0] ldac_cnt;

reg [0:23] dac_store;

reg we_d, en_d;

reg data_shift;

reg i_en, i_we;

reg [6:0] a_addrs, b_addrs, c_addrs, d_addrs, h_addrs;

reg config_go;

wire [0:23] config_data;

reg CS_ST, STAY = 1'b0, RUN = 1'b1;

reg [31:0] data_dac;

reg [31:0] i_dac_data;

reg [7:0] addr_cnt;

reg [9:0] i_r_addrs;

reg i_interrupt;

reg o_interrupt;

reg [12:0] interrupt_cnt;

reg done_en;

reg [7:0] config_in;

reg en_sh1, en_sh2;

wire en_sh_o;

reg [15:0] i_data_dac_in_1;

reg [15:0] i_data_dac_in_2;

reg [15:0] i_data_dac_in_3;

reg [15:0] i_data_dac_in_4;

reg data_go_1, data_go_2, data_go_3, data_go_4;

reg en_done;

assign sdi_o = data_in[15:0];

assign sclk = sck_o;

assign sync_n = cs_n;

assign ldac_n = ldac_in;

assign interrupt = o_interrupt;

assign sdi = sdi_in;

assign sdi_c = i_dac_data;

assign en_sh_o = (en_sh1 && ~en_sh2);

assign sdi_o = data_in[15:0];

assign sclk = sck_o;

assign sync_n = cs_n;

assign ldac_n = ldac_in;

assign interrupt = o_interrupt;

assign sdi = sdi_in;

// assign addr_i = i_r_addrs;

// assign sdi_c = sdi_out;

// assign st = STATE;

assign en_c = en_sh_o;

//assign we_c = i_we;

assign sdi_c = i_dac_data;

assign en_sh_o = (en_sh1 && ~en_sh2); //|| //(~en_sh1 && en_sh2));

always @(posedge sck_in or negedge rstn) begin

if(!rstn) begin

CS_ST <= RUN;

sck_cnt <= 0;

done <= 0;

end

else begin

case (CS_ST)

RUN : begin

done <= 0;

cs_n <= 0;

if(out_cnt == 23) begin

CS_ST <= STAY;

cs_n <= 1;

end

end

STAY : begin

done<=1;

cs_n <= 1;

sck_cnt <= sck_cnt + 1;

if (sck_cnt == 2) begin

CS_ST <= RUN;

sck_cnt <= 0;

done <= 1;

end

end

endcase

end

end

always @(posedge clk or negedge rstn) begin

if(!rstn) begin

i_en <= 0;

i_we <= 0;

i_addrs <= 0;

i_dac_data <= 0;

i_data_dac_in_1 <= 0;

i_data_dac_in_2 <= 0;

i_data_dac_in_3 <= 0;

i_data_dac_in_4 <= 0;

data_go_1 <= 0;

data_go_2 <= 0;

data_go_3 <= 0;

data_go_4 <= 0;

end

else begin

i_data_dac_in_1 <= data_dac_in_1;

i_data_dac_in_2 <= data_dac_in_2;

i_data_dac_in_3 <= data_dac_in_3;

i_data_dac_in_4 <= data_dac_in_4;

if(i_data_dac_in_1 != data_dac_in_1) begin

data_go_1 <= 1;

end

else if(i_data_dac_in_2 != data_dac_in_2) begin

data_go_2 <= 1;

end

else if(i_data_dac_in_3 != data_dac_in_3) begin

data_go_3 <= 1;

end

else if(i_data_dac_in_4 != data_dac_in_4) begin

data_go_4 <= 1;

end

else if(data_dac_en_1 && data_go_1) begin

i_dac_data <= {8'b0,CONFIG,3'b000,data_dac_in_1};

i_addrs <= a_addrs;

i_en <= 1;

if (en_done) begin

i_en <= 0;

data_go_1 <= 0;

end

end

else if(data_dac_en_2 && data_go_2) begin

// if(data_dac_en_2) begin

i_dac_data <= {8'b0,CONFIG,3'b001,data_dac_in_2};

i_we <= 1;

i_en <= 1;

i_addrs <= b_addrs + ADDR_DEPTH_DIV;

if (en_done) begin

i_en <= 0;

data_go_2 <= 0;

end

// end

end

else if(data_dac_en_3 && data_go_3) begin

//if(data_dac_en_3) begin

i_dac_data <= {8'b0,CONFIG,3'b010,data_dac_in_3};

i_we <= 1;

i_en <= 1;

i_addrs <= c_addrs + 2*ADDR_DEPTH_DIV;

if (en_done) begin

i_en <= 0;

data_go_3 <= 0;

end

end

else if(data_dac_en_4) begin

//if(data_dac_en_4) begin

i_dac_data <= {8'b0,CONFIG,3'b011,data_dac_in_4};

i_en <= ~i_en;

i_addrs <= d_addrs + 3*ADDR_DEPTH_DIV;

if (en_done) begin

i_en <= 0;

data_go_4 <= 0;

end

//end

end

end

end

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

en_sh1 <= 0;

en_sh2 <= 0;

en_done <= 0;

end

else begin

en_sh1 <= i_en;

en_sh2 <= en_sh1;

en_done <= 1;

if(!i_en) begin

en_done <= 0;

end

end

end

always @(negedge i_en or negedge rstn) begin

if (!rstn) begin

//i_addrs <= 0;

//h_addrs <= 0;

a_addrs <= 0;

b_addrs <= 0;

c_addrs <= 0;

d_addrs <= 0;

end

else begin

case (i_dac_data[18:16])

3'b000 : begin

a_addrs <= a_addrs +1;

end

3'b001 : begin

b_addrs <= b_addrs + 1;

end

3'b010 : begin

c_addrs <= c_addrs + 1;

end

3'b011 : begin

d_addrs <= d_addrs + 1;

end

endcase

end

end

dac_ram date_rx(

// Port A

.addra(i_addrs),

.clka(clk),

.dina(i_dac_data),

.ena(en_sh_o),

.wea(1'b1),

//Port B

.addrb(i_r_addrs),

.clkb(clk),

.doutb(data_in)

);

dac_ram data_o(

.addra(i_addrs),

.clka(clk),

.dina(i_dac_data),

.ena(en_sh_o),

.wea(1'b1),

//Port B

.addrb(read_addrs[10:0]),

.clkb(clkb),

.doutb(data_out)

);

endmodule

BRAM Trans

--- Updated ---

I couldn't write all the code by limit... but other side is working properly...

This is BRAM write side