m4rtinpf

Newbie

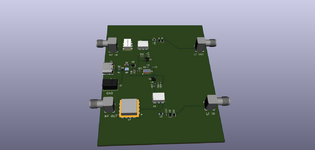

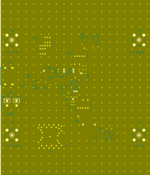

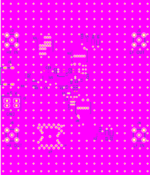

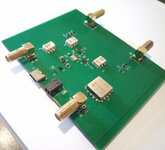

I've designed a PCB and was looking for some review and advice. The images are attached to this post.

The board is for an up/down frequency converter. Specifically, from 0-300 kHz to 400 MHz.

It's a simple design, the input signal gets multiplied by a 400 MHz square-wave (X1) by a mixer (U6 or U2). There are also two LPF and limiters.

Power comes from a USB connector or a terminal block and gets regulated down to 3.3 V by U5.

I'm planning to get it fabricated by JLCPCB, including the assembly of the SMT parts that they carry. I would have to hand-solder the ICs (or get someone to it). It's a two-layer board, and I need a single unit.

The size of the board is due to the enclosure I'm gonna use (Hammond 1455L801).

I have a few questions:

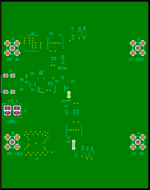

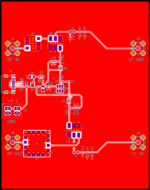

1. The ground plane is split in two places:

- The (amplified) clock signal (400 MHz square-wave) from U4 to C3, so VCC can get to the other side of this trace.

- The down-converted signal (<300 kHz) from U6 to L2, so this trace and the input signal (400 MHz) can cross.

Is this OK or using 0R resistors would be better?

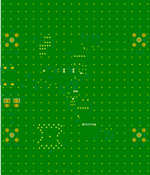

2. Should I remove the solder paste from the ICs that I'm not getting soldered by JLCPCB?

3. Are the vias connecting the top-layer filled zones to the ground plane enough and well placed (besides the ones under the ICs, just followed the datasheets for those)?

Thanks in advance for any help!

PS: There is a minor misalignment between layers in the images. It's because of a bug in Kicad that makes it so silkscreen is under copper when plotting to PDF, so I had to manually stack the individual layers.

The board is for an up/down frequency converter. Specifically, from 0-300 kHz to 400 MHz.

It's a simple design, the input signal gets multiplied by a 400 MHz square-wave (X1) by a mixer (U6 or U2). There are also two LPF and limiters.

Power comes from a USB connector or a terminal block and gets regulated down to 3.3 V by U5.

I'm planning to get it fabricated by JLCPCB, including the assembly of the SMT parts that they carry. I would have to hand-solder the ICs (or get someone to it). It's a two-layer board, and I need a single unit.

The size of the board is due to the enclosure I'm gonna use (Hammond 1455L801).

I have a few questions:

1. The ground plane is split in two places:

- The (amplified) clock signal (400 MHz square-wave) from U4 to C3, so VCC can get to the other side of this trace.

- The down-converted signal (<300 kHz) from U6 to L2, so this trace and the input signal (400 MHz) can cross.

Is this OK or using 0R resistors would be better?

2. Should I remove the solder paste from the ICs that I'm not getting soldered by JLCPCB?

3. Are the vias connecting the top-layer filled zones to the ground plane enough and well placed (besides the ones under the ICs, just followed the datasheets for those)?

Thanks in advance for any help!

PS: There is a minor misalignment between layers in the images. It's because of a bug in Kicad that makes it so silkscreen is under copper when plotting to PDF, so I had to manually stack the individual layers.