strennor

Advanced Member level 4

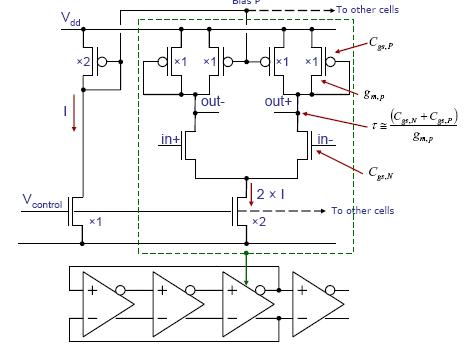

maneatis load

Hi,

For the biasing of Maneatis type load delay buffer, I think the biasing tail NMOS should be same size as the buffer tail NMOS.

Then the Vbp is equal to the min swing limit, since all the tail current is now in only one branch of the differential buffer.

But it is noted as half.

Why? Anyone can help?

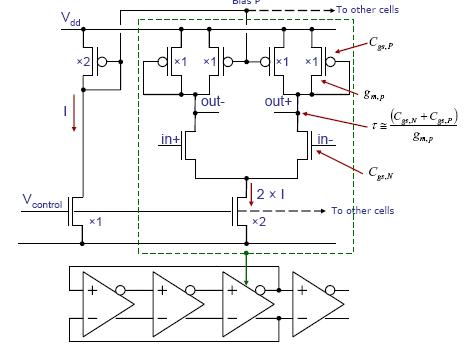

Hi,

For the biasing of Maneatis type load delay buffer, I think the biasing tail NMOS should be same size as the buffer tail NMOS.

Then the Vbp is equal to the min swing limit, since all the tail current is now in only one branch of the differential buffer.

But it is noted as half.

Why? Anyone can help?