stephane2788

Newbie

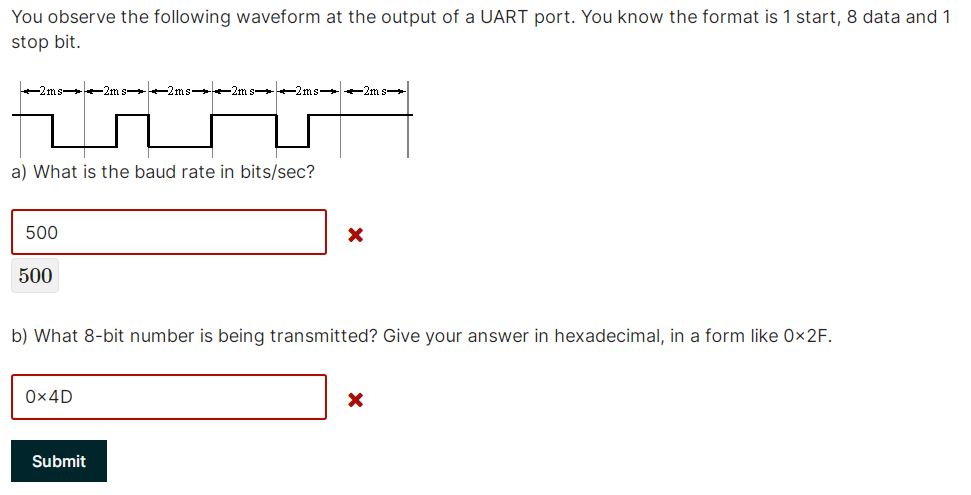

Hello, i'm doing a course on edX regarding UART and I have the below questions:

Can anybody help me understand why my values are wrong?

Can anybody help me understand why my values are wrong?

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

H - L - L - H - L - L - H - H - L - H - H - H -

IDLE-START-Bit0-Bit1-Bit2-Bit3-Bit4-Bit5-Bit6-Bit7-Stop-Idle-