dominoeff

Junior Member level 1

- Joined

- May 6, 2010

- Messages

- 17

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Location

- china-mainland

- Activity points

- 1,413

Hi Guys:

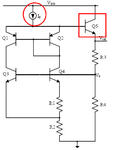

I am working on a bandgap circuit for a internal regulator in a DC-DC converter. The core circuit is a simple BROKAW bandgap circuit and i need a startup circuit for it.The problem is the input voltage is from 5~23 and the high voltage MOSFET my process provide have a max Gate-Source voltage(Vgs) of 5,while the max Base-Emitter(Vbe) voltage of 10.

Any suggestion or any paper reference is highly appreciated.

Thanks all.

Dominoeff

I am working on a bandgap circuit for a internal regulator in a DC-DC converter. The core circuit is a simple BROKAW bandgap circuit and i need a startup circuit for it.The problem is the input voltage is from 5~23 and the high voltage MOSFET my process provide have a max Gate-Source voltage(Vgs) of 5,while the max Base-Emitter(Vbe) voltage of 10.

Any suggestion or any paper reference is highly appreciated.

Thanks all.

Dominoeff