yefj

Advanced Member level 4

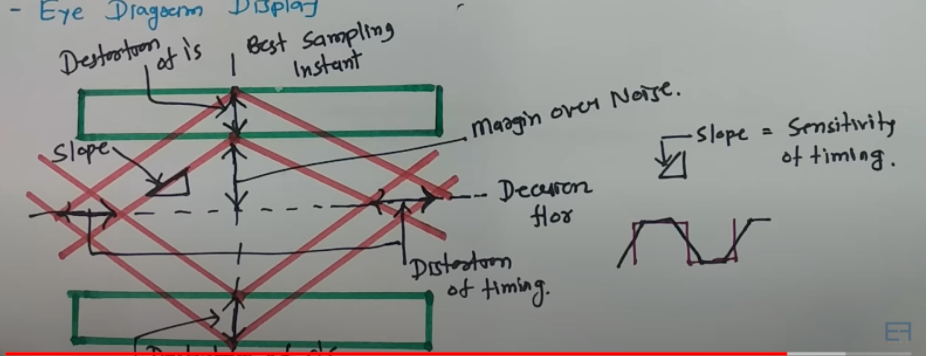

Hello,In the eye diagram bellow the top Wall distortion is caused by transmition line induction voltage drop.

the side wall low slope (big rise time)could be caused by high data rate .

why high data rate causes the slope to decrease thus getting high rise time?

Thanks.

the side wall low slope (big rise time)could be caused by high data rate .

why high data rate causes the slope to decrease thus getting high rise time?

Thanks.