andiaye33

Newbie

Hello,

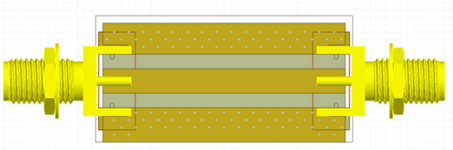

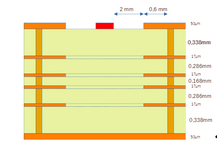

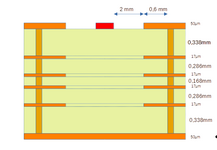

I’m simulation a Grounded CPW wint w=3.3mm, h=1.6 and g=2mm

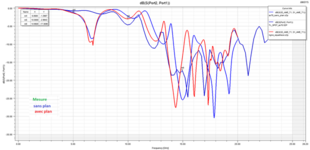

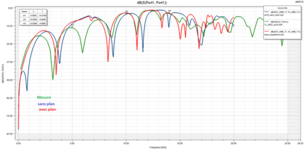

in HFSS and getting invalid results near 10GHz.

Can someone help me please

Any suggestions are welcomed.

I’m simulation a Grounded CPW wint w=3.3mm, h=1.6 and g=2mm

in HFSS and getting invalid results near 10GHz.

Can someone help me please

Any suggestions are welcomed.