asuprash

Newbie level 6

Hi All,

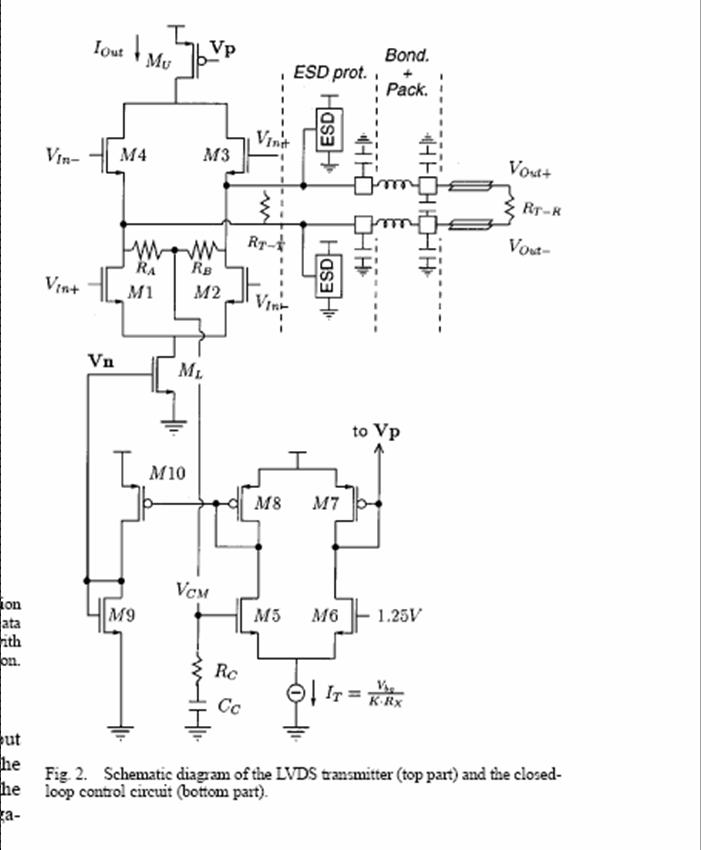

I was trying to understand the CMFB circuit by for the LVDS by Boni.

From the circuit can somebody explain how the CMFB circuit works.

I have some more CMFB circuits that I am trying to understand.

This is the first one.

If Vcm increases above 1.25 V the current in the left leg increases

and the current in the right leg decreases.

The reduced current in the right leg causes an increase in Vp

This Vp being fedback to the LVDS transmitter causes a decrease in Iout, which

will inturn would cause an increase in the Common Mode voltage.

This would not appear to cause decrease in the CM voltage as expected.

Can anyone through light on the apparent ambiguity ?

Also, can some one explain the need for the pole-zero compensation that

is provided and how it benefits the circuit.

Regards Prashanth

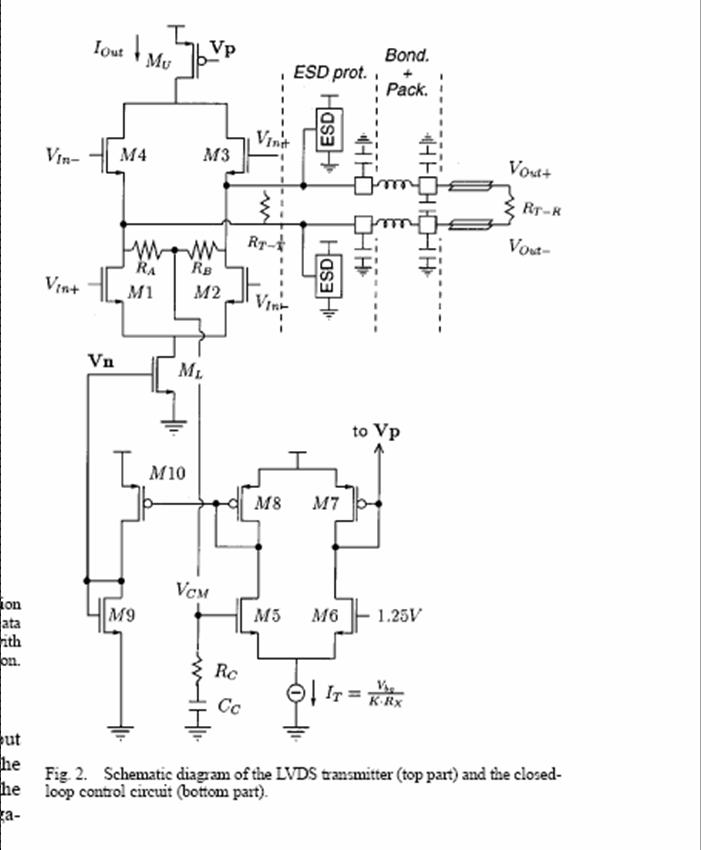

I was trying to understand the CMFB circuit by for the LVDS by Boni.

From the circuit can somebody explain how the CMFB circuit works.

I have some more CMFB circuits that I am trying to understand.

This is the first one.

If Vcm increases above 1.25 V the current in the left leg increases

and the current in the right leg decreases.

The reduced current in the right leg causes an increase in Vp

This Vp being fedback to the LVDS transmitter causes a decrease in Iout, which

will inturn would cause an increase in the Common Mode voltage.

This would not appear to cause decrease in the CM voltage as expected.

Can anyone through light on the apparent ambiguity ?

Also, can some one explain the need for the pole-zero compensation that

is provided and how it benefits the circuit.

Regards Prashanth