ConfusedAlways

Newbie

Hello, Im new to asic, and i encountered a strange case in using logical shift.

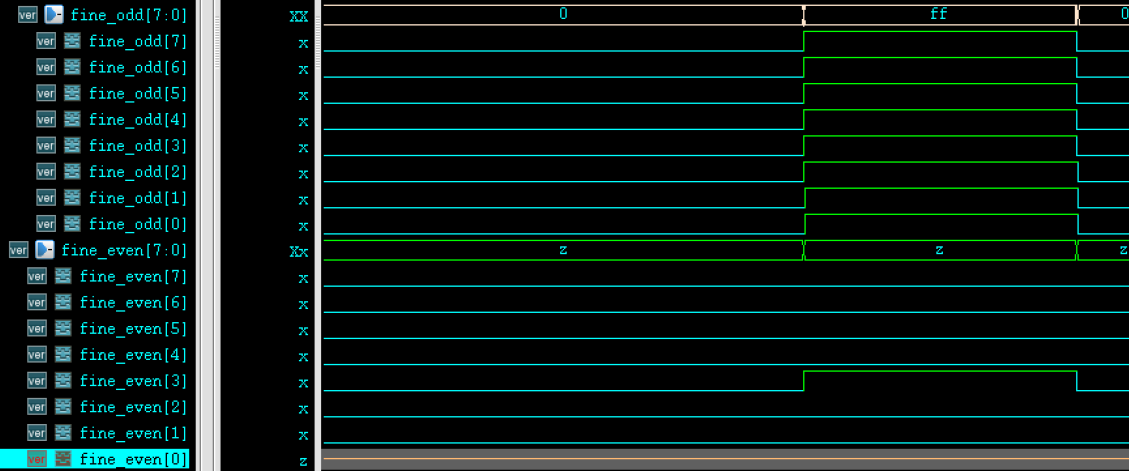

In my RTL, I had the left logical shift to make the var 2 times multiplied. During the simulation, the results are good. Once the sythesis had finished, the LSB of 'fine_even' became high z. Meanwhile 'fine_odd' did the same operation, but its result is correct.

At the beginning I set the width the same which is 8bit, i think maybe after shifting it was enlarged one bit. So I changed it to 7bit and 8bit, sadly the results are the same as the former one.

Related code and waveforms are attached below. Hope someone could help me with it. Thanks in advance.

In my RTL, I had the left logical shift to make the var 2 times multiplied. During the simulation, the results are good. Once the sythesis had finished, the LSB of 'fine_even' became high z. Meanwhile 'fine_odd' did the same operation, but its result is correct.

At the beginning I set the width the same which is 8bit, i think maybe after shifting it was enlarged one bit. So I changed it to 7bit and 8bit, sadly the results are the same as the former one.

Related code and waveforms are attached below. Hope someone could help me with it. Thanks in advance.

Code:

reg [7:0] fine_odd;

wire [6:0] out_odd_1;

reg [7:0] fine_even;

wire [6:0] out_even_1;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

fine_odd <= 'd0;

fine_even <= 'd0;

end else if (res_val_r)begin

fine_even <= ((out_even_1 -1) << 1);

fine_odd <= ((out_odd_1 -1) << 1) + 1;

end else begin

fine_even <= 'd0;

fine_odd <= 'd0;

end

end