arminb73

Junior Member level 3

Hello,

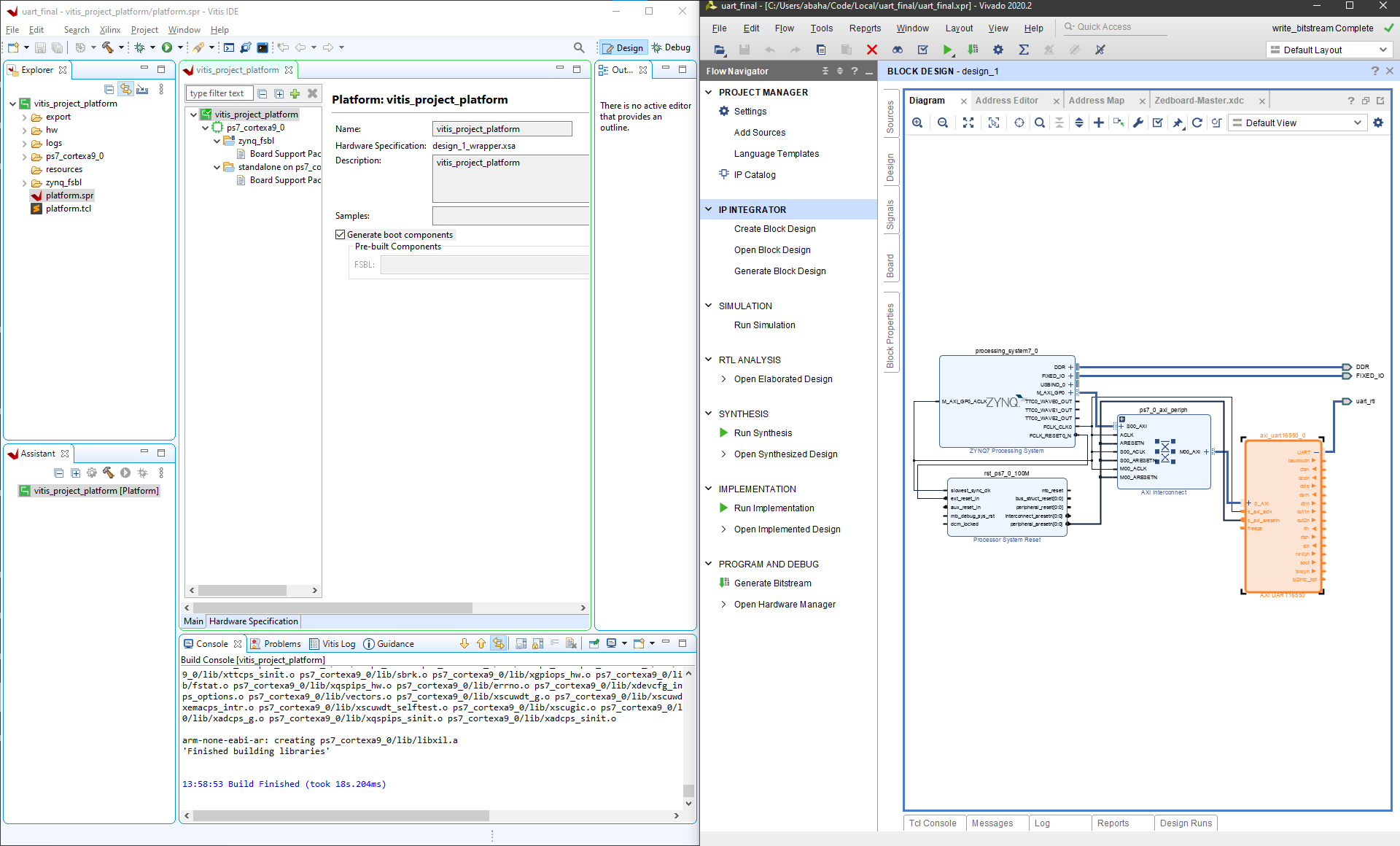

I am to use AXI UART16550 IP connected with ZYNQ7 PS to do some examples created by Xilinx in their software program Vitis: https://github.com/Xilinx/embeddedsw/tree/master/XilinxProcessorIPLib/drivers/uartns550

The main problem is I don't know how to add these examples to Vitis... The bitstream in Vivado has been created, and the platform project has also been created. All that is left is to add the code to Vitis.

I am to use AXI UART16550 IP connected with ZYNQ7 PS to do some examples created by Xilinx in their software program Vitis: https://github.com/Xilinx/embeddedsw/tree/master/XilinxProcessorIPLib/drivers/uartns550

The main problem is I don't know how to add these examples to Vitis... The bitstream in Vivado has been created, and the platform project has also been created. All that is left is to add the code to Vitis.