urian

Full Member level 3

Hi,there

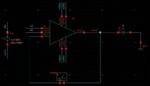

I have designed a 2-stage amp and used as voltage buffer,the vdd is 1.5v and vss is 0v.I want to test its open-loop gain,so I use the circuit as fig1(open-loop).The input is an diff.pairs,and the Vcm is set to 0.7v,their acm is set to 1v and dc voltage is set to 0v.Then I run AC analysis and sweep the frequency.When it finished,I click Direct plot->AC Gain&Phase and choose vout and vin+ as select points.The result gain is 51 dB.

Next ,I use the circuit like fig2(loop) to test the loop gain, and this time I only connect a vdc to the non-inverting input and set the dc voltage to 0,acm to 1,and connect vout and inverting input through an iprobe,then run the stb analysis.This time,stb summary tells me that that the gain is 9 dB,PM is 53. In my option ,since the feedback is configurated as voltage buffer,the open-loop gain will equal the loop gain,but the result shows that is not the case,I wonder whether the measure method I use is wrong.

Regards

I have designed a 2-stage amp and used as voltage buffer,the vdd is 1.5v and vss is 0v.I want to test its open-loop gain,so I use the circuit as fig1(open-loop).The input is an diff.pairs,and the Vcm is set to 0.7v,their acm is set to 1v and dc voltage is set to 0v.Then I run AC analysis and sweep the frequency.When it finished,I click Direct plot->AC Gain&Phase and choose vout and vin+ as select points.The result gain is 51 dB.

Next ,I use the circuit like fig2(loop) to test the loop gain, and this time I only connect a vdc to the non-inverting input and set the dc voltage to 0,acm to 1,and connect vout and inverting input through an iprobe,then run the stb analysis.This time,stb summary tells me that that the gain is 9 dB,PM is 53. In my option ,since the feedback is configurated as voltage buffer,the open-loop gain will equal the loop gain,but the result shows that is not the case,I wonder whether the measure method I use is wrong.

Regards