naalald

Full Member level 4

Hi,

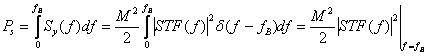

In the Shcreier book (2004), page 6, it's said that in delta-sigma converters since the signal is unchanged, i.e. there is only a delay for the signal, in the receiver no demodulation is needed and this is a great advantage of delta-sigma modulators comparing with delta modulators. Therefore, when defining the filter coefficients we usually try to set the Signal Transfer Function to (1/Z).

Now if we use delta-sigma modulators as ADCs there would be no receiver. Can we choose the filter coefficients so that the STF is not only a delay (1/z)?

In the Shcreier book (2004), page 6, it's said that in delta-sigma converters since the signal is unchanged, i.e. there is only a delay for the signal, in the receiver no demodulation is needed and this is a great advantage of delta-sigma modulators comparing with delta modulators. Therefore, when defining the filter coefficients we usually try to set the Signal Transfer Function to (1/Z).

Now if we use delta-sigma modulators as ADCs there would be no receiver. Can we choose the filter coefficients so that the STF is not only a delay (1/z)?