raychenchina

Newbie level 5

pcb adc grounding

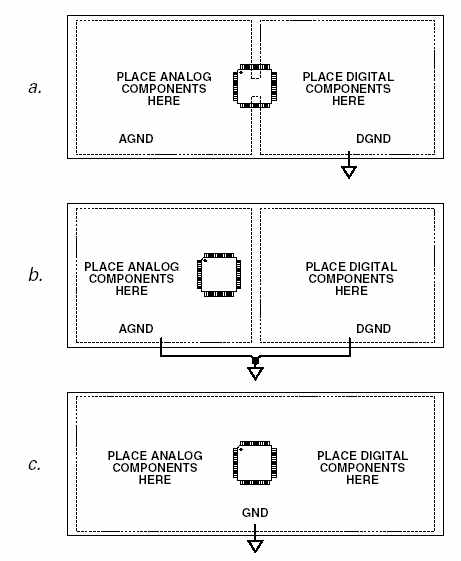

I have a question about ADC grounding. In the "Sensor Signal

Conditioning" published by ADI, the grounding is recommanded to

connect only in the power supply.

Also the ADC is regarded as analog device and is grounded to AGND.

My question is that if AGND and DGND is connected only in the power

supply, the current from DAC to buffer will flow through DGND - power

supply -AGND too. It's a big current loop, isn't it? Will it bring

noise to ADC's AGND?

Or I should use another ground method?

I can't upload the image, why?

I have a question about ADC grounding. In the "Sensor Signal

Conditioning" published by ADI, the grounding is recommanded to

connect only in the power supply.

Also the ADC is regarded as analog device and is grounded to AGND.

My question is that if AGND and DGND is connected only in the power

supply, the current from DAC to buffer will flow through DGND - power

supply -AGND too. It's a big current loop, isn't it? Will it bring

noise to ADC's AGND?

Or I should use another ground method?

I can't upload the image, why?