elahetal

Junior Member level 1

Hello Guys,

I have some problem and I really appreciate if you have a look at my circuit.Any comments, ideas, solutions,....are really appreciated!

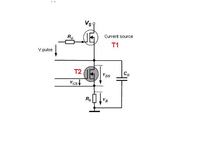

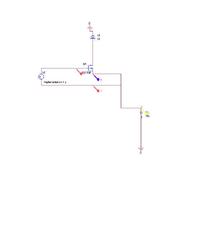

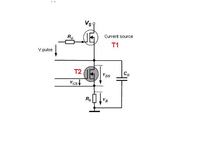

I have a circuit like Fig.1

The theory is:

The upper MOSFET gate is driven to active region by very short pulse width (not less than 300us) and low frequency or single pulse.

It is supposed to act as a current source to charge the capacitor across the power MOSFET.

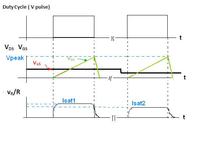

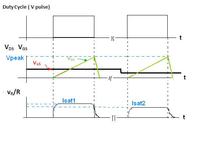

After the gate voltage is established in T2, T1 is driven to active region to act as a voltage controllable current source to provide constant current (I). Thus, the voltage vDS across the T2 increases in a linear fashion as C0 is charging with the constant current I. The drain current of T2 rises until it reaches saturation. T1 is then turned off slowly when the voltage vDS reaches the maximum allowed voltage (Vpeak). Then, the reverse operation occurs i.e. the voltage across C0 discharges through the channel of T2 toward zero. Fig. 2 shows the operation diagram.

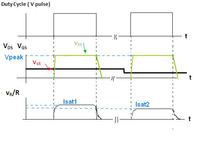

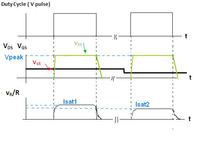

But what I see is the results in Fig 3.

( I have the same results both experimentally and PSpice simulation)

I have some problem and I really appreciate if you have a look at my circuit.Any comments, ideas, solutions,....are really appreciated!

I have a circuit like Fig.1

The theory is:

The upper MOSFET gate is driven to active region by very short pulse width (not less than 300us) and low frequency or single pulse.

It is supposed to act as a current source to charge the capacitor across the power MOSFET.

After the gate voltage is established in T2, T1 is driven to active region to act as a voltage controllable current source to provide constant current (I). Thus, the voltage vDS across the T2 increases in a linear fashion as C0 is charging with the constant current I. The drain current of T2 rises until it reaches saturation. T1 is then turned off slowly when the voltage vDS reaches the maximum allowed voltage (Vpeak). Then, the reverse operation occurs i.e. the voltage across C0 discharges through the channel of T2 toward zero. Fig. 2 shows the operation diagram.

But what I see is the results in Fig 3.

( I have the same results both experimentally and PSpice simulation)