Eicalos

Newbie level 5

I have the assignment.

Design Schematic with Quartus II

a) 1-bit Binary Adder (Full Adder) use AND2/OR2/INV and create symbol (Schematic Symbol) name "FA"

b) 8-bit Binary Adder use Full Adder from a) create (Schematic Symbol) name "ADD8"

c) 8-bit Register use D-Type Flip-Flop create Schematic Symbol) name "REG8"

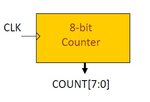

d) 8-bit Binary Counter use symbol from b) and c)

a,b,c. I can did it. But d I don't know how to integrate it.

Plz help me!!!

Design Schematic with Quartus II

a) 1-bit Binary Adder (Full Adder) use AND2/OR2/INV and create symbol (Schematic Symbol) name "FA"

b) 8-bit Binary Adder use Full Adder from a) create (Schematic Symbol) name "ADD8"

c) 8-bit Register use D-Type Flip-Flop create Schematic Symbol) name "REG8"

d) 8-bit Binary Counter use symbol from b) and c)

a,b,c. I can did it. But d I don't know how to integrate it.

Plz help me!!!