danadakk

Advanced Member level 6

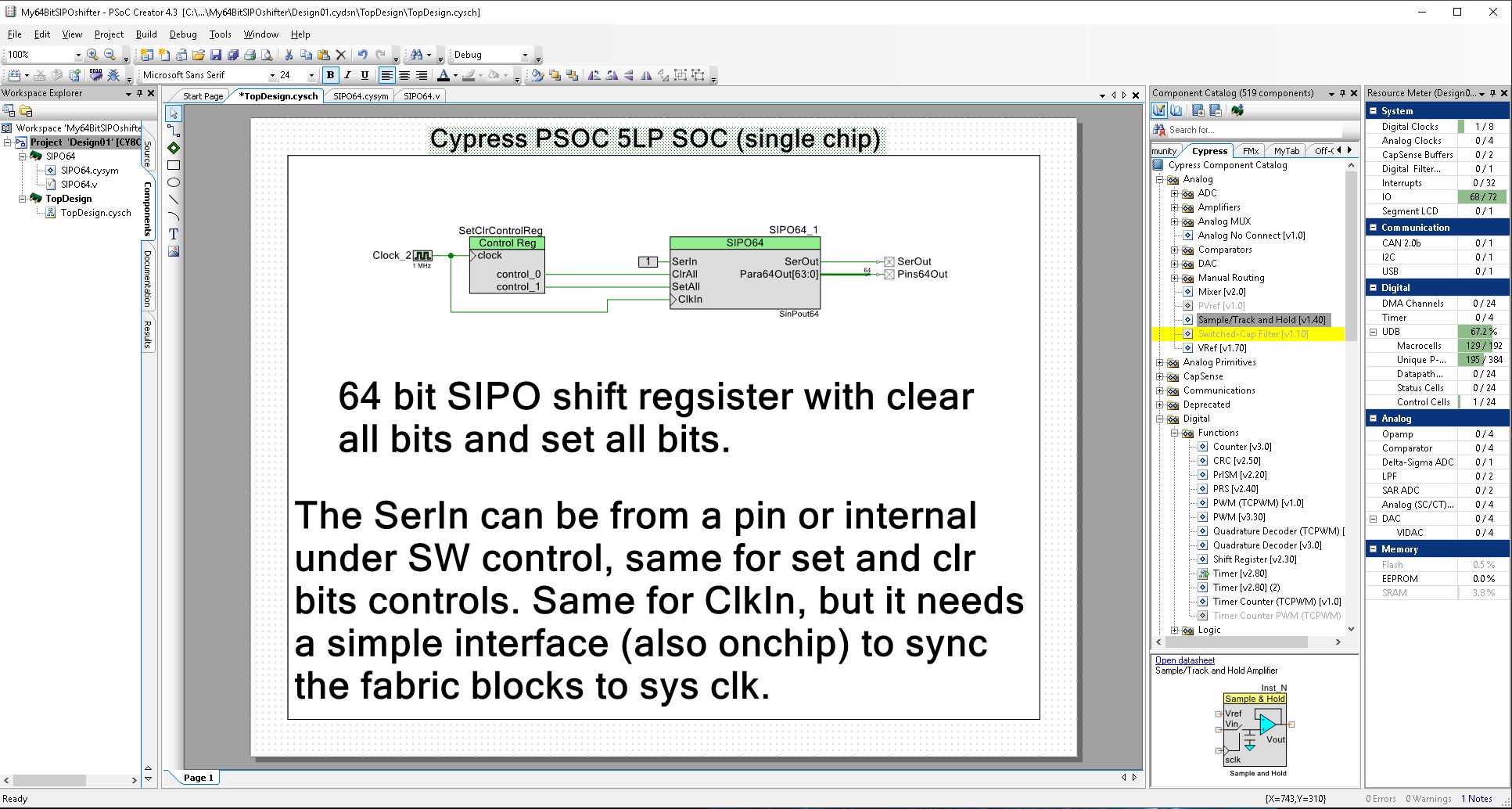

Occasionally I need long shift registers. This is a design done on a single PSOC

chip using verilog.

Its 64 bits wide, SIPO, with controls to clear or set all bits.

Notice many additional chip resources went un used that are availble for other tasks,

like COM, Timer, Counter, Analog,.....see right hand window of resources used/left.

This particular design eats up most of the I/O, so using additional onchip resources, for example

if you wanted to use its LCD capability, would be challenged by the amount of I/O consumed by

the shift register. The shift register could also be expanded using another chip programmed

same way.

Note chip has ARM M3 in it for general purpose programming.

The verilog code fairly simple, looks like (you first generate the symbol with a wizard) -

Note if you are not a coder this could have been done via schematic capture just dragging and

dropping onto canvas 64 D FF's from its resource catalog and wiring them up. But very tedious

in this case.

Regards, Dana.

chip using verilog.

Its 64 bits wide, SIPO, with controls to clear or set all bits.

Notice many additional chip resources went un used that are availble for other tasks,

like COM, Timer, Counter, Analog,.....see right hand window of resources used/left.

This particular design eats up most of the I/O, so using additional onchip resources, for example

if you wanted to use its LCD capability, would be challenged by the amount of I/O consumed by

the shift register. The shift register could also be expanded using another chip programmed

same way.

Note chip has ARM M3 in it for general purpose programming.

The verilog code fairly simple, looks like (you first generate the symbol with a wizard) -

C-like:

//`#start header` -- edit after this line, do not edit this line

// ========================================

//

// Copyright YOUR COMPANY, THE YEAR

// All Rights Reserved

// UNPUBLISHED, LICENSED SOFTWARE.

//

// CONFIDENTIAL AND PROPRIETARY INFORMATION

// WHICH IS THE PROPERTY OF your company.

//

// ========================================

`include "cypress.v"

//`#end` -- edit above this line, do not edit this line

// Generated on 06/07/2020 at 15:00

// Component: SIPO64

module SIPO64 (

output reg [63:0] Para64Out,

output reg SerOut,

input ClkIn,

input ClrAll,

input SerIn,

input SetAll

);

//`#start body` -- edit after this line, do not edit this line

reg [63:0] SReg;

always @(posedge ClkIn) begin

if ( ( SetAll == 1'b1 ) || ( ClrAll == 1'b1 ) ) begin

if ( SetAll == 1'b1 )

SReg <= 64'hFFFFFFFFFFFFFFFF; // Set all bits in Shift Reg to "1"s

else if ( ClrAll == 1'b1 )

SReg <= 64'h0000000000000000; // Clr all bits in Shift Reg to "0"s

end else begin

SReg <= {SerIn, SReg[63:1]}; // Shift right 1 bit and input the Serial in Bit

Para64Out <= SReg;

SerOut <= SReg[0];

end

end

//`#end` -- edit above this line, do not edit this linedropping onto canvas 64 D FF's from its resource catalog and wiring them up. But very tedious

in this case.

Regards, Dana.

Last edited: