Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

the output inverted value is delayed for some seconds

In normal situations, only one inverter is needed.

But when there are 3 in a row:

* Sometimes the designer adds more gates in order to use up spare gates on an IC.

* Sometimes the initial signal rises or falls slowly. Although one gate supposedly will have a clean output that transitions quickly, the designer might add another gate just in case. Then he must add a third NOT gate to invert the signal back to its polarity as it was after the first NOT gate.

* Sometimes a designer needs just a tiny delay in the signal. Each gate contains numerous transistors. The propagation delays add up to a tiny amount.

* The schematic does not show additional connections, but it would be easy to tap in between the gates to obtain a second signal. Example, an out-of-phase clock signal.

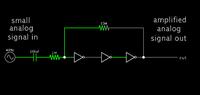

* You mention an amplifier. There is a way to use digital gates in an analog application. 3 inverters and 2 resistors form an amplifier. It doesn't work in the simulator, but it works with real components. The 4069 inverter IC is particularly recommended for this.

* Sometimes the initial signal rises or falls slowly. Although one gate supposedly will have a clean output that transitions quickly, the designer might add another gate just in case. Then he must add a third NOT gate to invert the signal back to its polarity as it was after the first NOT gate.