shabazsyed

Junior Member level 3

Hello Guys ,

I am trying to verify my Hand Calculations and Spice Results. But the simulated results are less than Calculated. Its TSMC .35um Tech.

Spice Code.

***8

vdg vds 0 dc 5

vff vgs 0 dc 5

vdum vds b dc 0

mn1 b vgs 0 0 nmos w=1u l=.4u

.include moslh.md

.dc vdg 0 5 .00005 vff 1 5 1

.control

reset

run

plot i(vdum)

.endc

.end

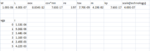

My Calculated Results

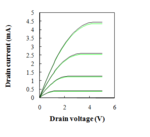

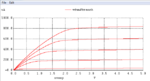

Simulated Results.

Y is Calculated Result differing From Spice Results?

Any Suggestions.

Eagerly Waiting For Some replies.

Thanx

I am trying to verify my Hand Calculations and Spice Results. But the simulated results are less than Calculated. Its TSMC .35um Tech.

Spice Code.

***8

vdg vds 0 dc 5

vff vgs 0 dc 5

vdum vds b dc 0

mn1 b vgs 0 0 nmos w=1u l=.4u

.include moslh.md

.dc vdg 0 5 .00005 vff 1 5 1

.control

reset

run

plot i(vdum)

.endc

.end

My Calculated Results

Simulated Results.

Y is Calculated Result differing From Spice Results?

Any Suggestions.

Eagerly Waiting For Some replies.

Thanx