Aritra17

Junior Member level 3

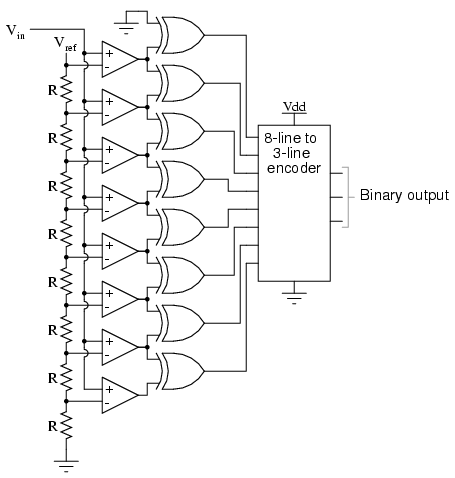

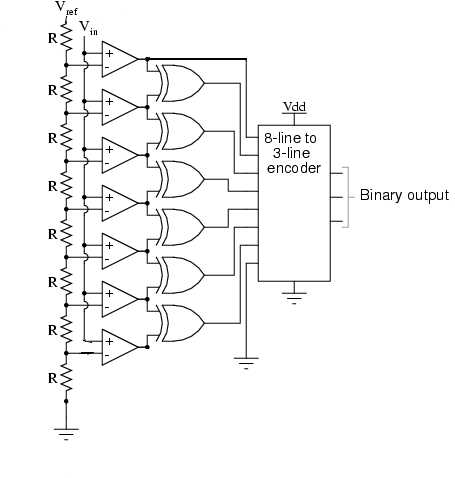

i need a 3 bit cmos encoder circuit with all the 8 inputs

i have created a 7 input encoder using rom design bt i need to have the '000' condition also

please help

i have created a 7 input encoder using rom design bt i need to have the '000' condition also

please help