eem2am

Banned

Hello,

Will we damage our Freescale MC9S08AC60CFGE microcontroller by driving a FET from a microcontroller output pin, with no series resistor?

We are powering solenoids via switch-mode solenoid drivers which comprise FETs being driven directly from a microcontroller.

-as stated , the FET gates are being driven directly from the microcontroller pins, with no series resistor used. (-the microcontroller is supplied from 5V)

Here is the schematic:

SCHEMATIC:

https://i53.tinypic.com/1zm1j08.jpg

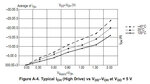

Here is the gate charge current…….please notice that it goes up to 450mA , -though the gate charge pulse is only for 103ns (the switching frequency is 20KHz)

…I represented the output resistance of the microcontroller pin as 5R, though in truth , I don’t know what it is, and the datasheet does not state it.

GATE CHARGE CURRENT:

https://i52.tinypic.com/9a1yyr.jpg

Page 304 of the MC9S08AC60CFGE microcontroller datasheet states that the maximum instantaneous current allowable in a microcontroller pin is 25mA

Page 304 of MC9S08AC60CFGE microcontroller datasheet:

https://i51.tinypic.com/4rtj00.jpg

Also of interest , is that page 307 of the MC9S08AC60CFGE microcontroller datasheet states that the latch up current is 100mA…….so does this mean that we will be risking latch-up?....since our gate drive current pulses go up to 450mA…..

Page 307 of MC9S08AC60CFGE microcontroller datasheet:

https://i51.tinypic.com/fmq61k.jpg

MICROCONTROLLER DATASHEET (Freescale MC9S08AC60CFGE):

https://cache.freescale.com/files/microcontrollers/doc/data_sheet/MC9S08AC60.pdf?fsrch=1&sr=5

FET DATASHEET (STB16NF06LT4):

https://www.st.com/internet/com/TECHNICAL_RESOURCES/TECHNICAL_LITERATURE/DATASHEET/CD00002847.pdf

Will we damage our Freescale MC9S08AC60CFGE microcontroller by driving a FET from a microcontroller output pin, with no series resistor?

We are powering solenoids via switch-mode solenoid drivers which comprise FETs being driven directly from a microcontroller.

-as stated , the FET gates are being driven directly from the microcontroller pins, with no series resistor used. (-the microcontroller is supplied from 5V)

Here is the schematic:

SCHEMATIC:

https://i53.tinypic.com/1zm1j08.jpg

Here is the gate charge current…….please notice that it goes up to 450mA , -though the gate charge pulse is only for 103ns (the switching frequency is 20KHz)

…I represented the output resistance of the microcontroller pin as 5R, though in truth , I don’t know what it is, and the datasheet does not state it.

GATE CHARGE CURRENT:

https://i52.tinypic.com/9a1yyr.jpg

Page 304 of the MC9S08AC60CFGE microcontroller datasheet states that the maximum instantaneous current allowable in a microcontroller pin is 25mA

Page 304 of MC9S08AC60CFGE microcontroller datasheet:

https://i51.tinypic.com/4rtj00.jpg

Also of interest , is that page 307 of the MC9S08AC60CFGE microcontroller datasheet states that the latch up current is 100mA…….so does this mean that we will be risking latch-up?....since our gate drive current pulses go up to 450mA…..

Page 307 of MC9S08AC60CFGE microcontroller datasheet:

https://i51.tinypic.com/fmq61k.jpg

MICROCONTROLLER DATASHEET (Freescale MC9S08AC60CFGE):

https://cache.freescale.com/files/microcontrollers/doc/data_sheet/MC9S08AC60.pdf?fsrch=1&sr=5

FET DATASHEET (STB16NF06LT4):

https://www.st.com/internet/com/TECHNICAL_RESOURCES/TECHNICAL_LITERATURE/DATASHEET/CD00002847.pdf