cannibol_90

Member level 5

Hi,

We are trying to simulate a CMOS Ring Oscillator using AWR AO. We are amateurs and only know the basic design equations for designing one.

We are using 180nm technology and the maximum VDD allowed is 1.8V (as said by our boss). But the problem is that we are getting oscillations only at approximately 5V bias.

No matter how much we change the widths and lengths the oscillations occur only at a bias voltage of 5V. We are using BSIM3 version for the NMOS and PMOS. We understand that the problem is with the MOSFET model used.

We tried the AWR example of Push Push Oscillator and the output was obtained beautifully at the desired voltage.

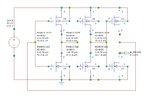

Please help us in understanding what parameters or model of the MOSFET has to be changed so as to obtain an output at the desired voltage. We are attaching the schematic and simulated results.

Please Help!

We are trying to simulate a CMOS Ring Oscillator using AWR AO. We are amateurs and only know the basic design equations for designing one.

We are using 180nm technology and the maximum VDD allowed is 1.8V (as said by our boss). But the problem is that we are getting oscillations only at approximately 5V bias.

No matter how much we change the widths and lengths the oscillations occur only at a bias voltage of 5V. We are using BSIM3 version for the NMOS and PMOS. We understand that the problem is with the MOSFET model used.

We tried the AWR example of Push Push Oscillator and the output was obtained beautifully at the desired voltage.

Please help us in understanding what parameters or model of the MOSFET has to be changed so as to obtain an output at the desired voltage. We are attaching the schematic and simulated results.

Please Help!