allennlowaton

Full Member level 5

Hello EDA fellows.

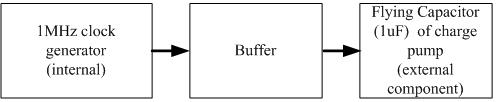

I want to ask you something about clock driving for my 1uF flying capacitor. I'm making my LED driver IC now and my problem is how can I drive my 1uF external capacitor with my internally produced 1MHz clock. I'm afraid taper buffer would be very very large if I'm going to use it.

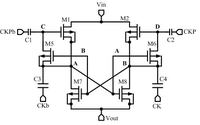

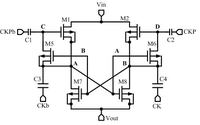

Below is the circuit diagram of my charge pump.

Thank you very much for your time.

Sincerely,

Allenn

I want to ask you something about clock driving for my 1uF flying capacitor. I'm making my LED driver IC now and my problem is how can I drive my 1uF external capacitor with my internally produced 1MHz clock. I'm afraid taper buffer would be very very large if I'm going to use it.

Below is the circuit diagram of my charge pump.

Thank you very much for your time.

Sincerely,

Allenn