chandlerbing65nm

Member level 5

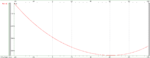

I have a problem solving for a stable 0.4~.5 vref in my simulations. All transistors are saturated except for start-up.

My current reference in pmos opamp is 500nA, and 60+db gain opamp with 60* PM.

VDD = 1.2V

I already solved the value of resistors. I cant really get a stable output, some expert can help?

I have attached the temperature and VDD variation results as well as my circuit.

My current reference in pmos opamp is 500nA, and 60+db gain opamp with 60* PM.

VDD = 1.2V

I already solved the value of resistors. I cant really get a stable output, some expert can help?

I have attached the temperature and VDD variation results as well as my circuit.