J.Yuan

Junior Member level 1

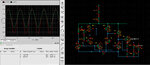

I trying to measure Power Supply Rejection Ratio (PSRR) of LDO,

but the output ac voltage is bigger than the input ac voltage.

the output ac voltage should be smaller than the input ac voltage.

base on the formula, PSRR = 20log(Vout,ripple/Vin,ripple ) in dB.

is there any wrong with my circuit construction for PSRR simulation?