mwb

Junior Member level 2

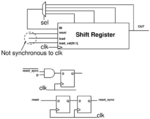

I have synthesized a shift-register with feedback and adjustable feedback taps. I have two questions:

1) The SR has a load and a reset, both synchronous. Both load and reset signals come from off-chip and are not synchronous to the clk so I have sent them both through FIFO synchronizers. My question is, should I be doing a "set_false_path -from reset" (and likewise for load) in the timing constraints? The job of the synchronizers is to make sure that the reset/load signals don't violate hold time of the DFFs so my inclination is to not ignore the path. My worry is that this will cause p+r to try to find a difficult route.

2) As I said, the SR uses feedback meaning, I can choose a tap, (not any tap only 31,32,63,64) , and feed that back into the input. The feedback tap is also the output that goes to another part of the circuit. A few years ago, I built this circuit and taped it out as part of a bigger design. At high frequencies(>1GHz) it performed well, however, lower at lower frequencies(200MHz), the output signal would "die" after 30 seconds. The theory was there was not enough/too much decap in the clock buffer but I have no real way to verify this. Any ideas? Any pitfalls with feedback that I should be aware of?

Thanks.

1) The SR has a load and a reset, both synchronous. Both load and reset signals come from off-chip and are not synchronous to the clk so I have sent them both through FIFO synchronizers. My question is, should I be doing a "set_false_path -from reset" (and likewise for load) in the timing constraints? The job of the synchronizers is to make sure that the reset/load signals don't violate hold time of the DFFs so my inclination is to not ignore the path. My worry is that this will cause p+r to try to find a difficult route.

2) As I said, the SR uses feedback meaning, I can choose a tap, (not any tap only 31,32,63,64) , and feed that back into the input. The feedback tap is also the output that goes to another part of the circuit. A few years ago, I built this circuit and taped it out as part of a bigger design. At high frequencies(>1GHz) it performed well, however, lower at lower frequencies(200MHz), the output signal would "die" after 30 seconds. The theory was there was not enough/too much decap in the clock buffer but I have no real way to verify this. Any ideas? Any pitfalls with feedback that I should be aware of?

Thanks.