diego.fan

Member level 3

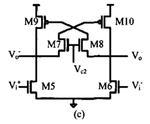

In this paper, there are two sentences:

1. The maximum voltage observed at the gate of M9 is Vg(max)=Vc2-Vtn,. As Vc2 increases the average, gate voltage of the PMOS transistors increases.

2. Large M6 and M10 increases the Vg(max) of M9 and MI0 and hence extends the tuning range.

I'm confused by these two sentences. Which one decides Vg(max) of M9?