sherif96

Member level 4

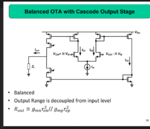

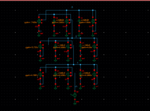

I am designing a balanced ota with cascode output stage attached is my ota schemaitc, however I am still new to IC designing I did not get the hang of the basics yet, such as transistors dimensions and current scaling, I am trying to bias all the transistors in the circuit however the top left and top bottom are always in triode region, I am using a Vdd of 1.2 maximum, what transistors dimensions and V for the two cascodes should I use in such circuit to bias the whole circuit ?