mohamedhany

Newbie level 4

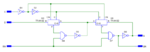

I designed a d flip flop using cadence. I want it to work with the rising edge of the clock (pulse wave). Any idea on how to do that?

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.