bwarlord01

Junior Member level 3

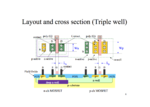

Hi guys, i just wanna ask, what layers should i add in my NMOS Layout in order to prevent short circuit from other NMOS Devices, since these NMOS Devices have different bulk potentials.

I am using TSMC 65nm CMOS Process Technology.

I am a bit confused about these NWELL, PWELL, DNWELL, and i dont know what to do to make my layout work

I am using TSMC 65nm CMOS Process Technology.

I am a bit confused about these NWELL, PWELL, DNWELL, and i dont know what to do to make my layout work