tenso

Advanced Member level 4

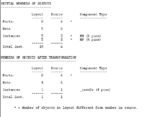

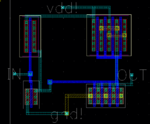

I am using calibre's LVS utility for the first time and I am getting some errors. I was trying to follow the PDK design flow document with a TSMC kit. I am attaching a screenshot of the layout (which was generated through Cadence's Chip Assembly Router), the schematic with which it is being compared to and the LVS report from calibre. The circuit itself is a 2 stage buffer.

Apparently there are no ports in the layout even though I have included the labels for the IN, OUT, VDD and GND pins. Also both the multifinger transistors are showing up as 4 transistors, so my instance numbers are also different.

Apparently there are no ports in the layout even though I have included the labels for the IN, OUT, VDD and GND pins. Also both the multifinger transistors are showing up as 4 transistors, so my instance numbers are also different.