dipin

Full Member level 4

hi,

i implemented a NCO(numerically controlled oscillator) in fpga.

according to the equation , its frequency f = (controllword x f clock)/ 2^N;

here i am using control word =50 (step size);f clock= 65Mhz; N=12 bits.. so frequency must be around 793khz.

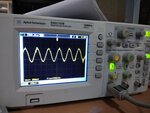

but i am getting frequency around 990 khz, when i use a oscilloscope to measure it ...

can anybody give any suggestions on this ??

any help is really appreciated

Thanks and Regards

i implemented a NCO(numerically controlled oscillator) in fpga.

according to the equation , its frequency f = (controllword x f clock)/ 2^N;

here i am using control word =50 (step size);f clock= 65Mhz; N=12 bits.. so frequency must be around 793khz.

but i am getting frequency around 990 khz, when i use a oscilloscope to measure it ...

can anybody give any suggestions on this ??

any help is really appreciated

Thanks and Regards