T

treez

Guest

Hello,

Please assist us in solving our Common mode noise problem?

We have designed an Offline 240VAC LED driver which is linear regulator based. (86% efficient).

It does however contain a 1W Buck converter for its bias supply.

The schematic of the salient parts, and the filter components, is as attached in the pdf.

For cost reasons, we are not allowing ourselves to use any through hole components on the PCB. We are also not allowed any custom made components (only offtheshelf allowed). We are also not allowed to take an earth wire connection to the PCB, as its more cost due to the greater assembly effort. (the Earth wire does, however, connect to the earthed heatsink on which the PCB sits, and is held onto by metal screws)

For the following Conducted EMC scans, we changed the values of some of the filter components shown in the pdf…….changing the Inductor values to try and get it to pass conducted EMC….

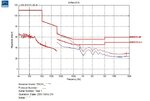

We started off with scan A. The filter values for this were as in the schematic.

Scan A is a fail around 150Khz.

Therefore we changed the damping resistors (R2,R3) to 1k, as in scan B, and then it was still a fail at 150kHz, but less badly failing than A.

Therefore we kept the 1k resistors for R2 and R3, and then increased L3 from 47uH to 100uH as in Scan C. However, this was worse than scan B at the failure frequency of 150kHz. That is, increasing the filter inductance, made the conducted scan worse. This made us realise that our problem is predominantly a common mode problem. 150kHz is not a usual frequency for a common mode problem, but as you know, the 150kHz is simply the frequency of the” envelope” which comprises the much higher frequency common mode disturbances.

Anyway…we then reduced L3 to 22uH and finally got it to pass (hoorah!) as in scan D.

However, the readout for scan D strangely says it’s a fail at 150kHz because it recorded exactly 66dBuV and that is exactly what the limit line is at. –So the official readout said that we failed by zero dBuV (!!!).

Anyway, in a desperation to get further below the limit line, we then kept L3=22uH, and kept R2,R3=1k, but increased L4 and L5 each from 100uH to 150uH. This is shown in scan E.

..However, this is worse than scan D. –It fails badly around 500kHz. Again it showed that increasing the filter inductance, made the results worse.

However, decreasing L4 and L5 each from 100uH down to 47uH also made the result worse. So therefore we have currently stuck with R2 & R3=1k, L3=22uH, L4 & L5 = 100uH. (ie scan D) The rest is as in the schematic shown.

However, as scan D shows, we are too close to the limit line, and need to reduce the noise more….

Buck switching node:

We believe that much of the problem common mode noise, is emitting from the switching node of the 1W Buck converter. (we know this from previously reducing the switching node copper size and taking EMC scans).

Shielding the switching node from the earthed heatsink:

For the above scans (A-F), we also shielded the Buck’s switching node copper from the Earthed Heatsink by laying copper pours in the internal and bottom PCB layers below the switching node copper. The shielding layers are connected to circuit ground. –We are now wondering if this is a mistake? In fact, we wonder if we should have used the 13V rail net for the shielding layers? The problem with using circuit ground as the shielding layers , is that there is a large circuit ground copper pour over most of the bottom layer of the PCB, which lies on the earthed heatsink. As such, we fear that having circuit ground as our shield for our switching node, is actually in some way injecting too much switching node noise into the earthed heatsink and exacerbating our common mode noise problem? Should we instead use the 13V rail net as our shielding layer? (to go between the switching node and the earthed heatsink).

EMC capacitors coupling to Earth ground.

As discussed, we don’t have an earth wire connection to the PCB. However, the PCB is held onto the earthed heatsink by metal screws. We are thereby wondering if we can thereby do the following so as to further decrease our common mode noise problem?......We could plate under the head of one of the screws with bare PCB copper. In this way, we would get some PCB copper which was directly connected to Earth ground. We could then couple the 13V rail net (ie a ‘quiet’ node) to this Earthed copper by using a 100pF capacitor. (4kV,2225,X7R)

Do you think that this would help decrease our common mode noise problem?

Please assist us in solving our Common mode noise problem?

We have designed an Offline 240VAC LED driver which is linear regulator based. (86% efficient).

It does however contain a 1W Buck converter for its bias supply.

The schematic of the salient parts, and the filter components, is as attached in the pdf.

For cost reasons, we are not allowing ourselves to use any through hole components on the PCB. We are also not allowed any custom made components (only offtheshelf allowed). We are also not allowed to take an earth wire connection to the PCB, as its more cost due to the greater assembly effort. (the Earth wire does, however, connect to the earthed heatsink on which the PCB sits, and is held onto by metal screws)

For the following Conducted EMC scans, we changed the values of some of the filter components shown in the pdf…….changing the Inductor values to try and get it to pass conducted EMC….

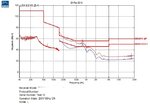

We started off with scan A. The filter values for this were as in the schematic.

Scan A is a fail around 150Khz.

Therefore we changed the damping resistors (R2,R3) to 1k, as in scan B, and then it was still a fail at 150kHz, but less badly failing than A.

Therefore we kept the 1k resistors for R2 and R3, and then increased L3 from 47uH to 100uH as in Scan C. However, this was worse than scan B at the failure frequency of 150kHz. That is, increasing the filter inductance, made the conducted scan worse. This made us realise that our problem is predominantly a common mode problem. 150kHz is not a usual frequency for a common mode problem, but as you know, the 150kHz is simply the frequency of the” envelope” which comprises the much higher frequency common mode disturbances.

Anyway…we then reduced L3 to 22uH and finally got it to pass (hoorah!) as in scan D.

However, the readout for scan D strangely says it’s a fail at 150kHz because it recorded exactly 66dBuV and that is exactly what the limit line is at. –So the official readout said that we failed by zero dBuV (!!!).

Anyway, in a desperation to get further below the limit line, we then kept L3=22uH, and kept R2,R3=1k, but increased L4 and L5 each from 100uH to 150uH. This is shown in scan E.

..However, this is worse than scan D. –It fails badly around 500kHz. Again it showed that increasing the filter inductance, made the results worse.

However, decreasing L4 and L5 each from 100uH down to 47uH also made the result worse. So therefore we have currently stuck with R2 & R3=1k, L3=22uH, L4 & L5 = 100uH. (ie scan D) The rest is as in the schematic shown.

However, as scan D shows, we are too close to the limit line, and need to reduce the noise more….

Buck switching node:

We believe that much of the problem common mode noise, is emitting from the switching node of the 1W Buck converter. (we know this from previously reducing the switching node copper size and taking EMC scans).

Shielding the switching node from the earthed heatsink:

For the above scans (A-F), we also shielded the Buck’s switching node copper from the Earthed Heatsink by laying copper pours in the internal and bottom PCB layers below the switching node copper. The shielding layers are connected to circuit ground. –We are now wondering if this is a mistake? In fact, we wonder if we should have used the 13V rail net for the shielding layers? The problem with using circuit ground as the shielding layers , is that there is a large circuit ground copper pour over most of the bottom layer of the PCB, which lies on the earthed heatsink. As such, we fear that having circuit ground as our shield for our switching node, is actually in some way injecting too much switching node noise into the earthed heatsink and exacerbating our common mode noise problem? Should we instead use the 13V rail net as our shielding layer? (to go between the switching node and the earthed heatsink).

EMC capacitors coupling to Earth ground.

As discussed, we don’t have an earth wire connection to the PCB. However, the PCB is held onto the earthed heatsink by metal screws. We are thereby wondering if we can thereby do the following so as to further decrease our common mode noise problem?......We could plate under the head of one of the screws with bare PCB copper. In this way, we would get some PCB copper which was directly connected to Earth ground. We could then couple the 13V rail net (ie a ‘quiet’ node) to this Earthed copper by using a 100pF capacitor. (4kV,2225,X7R)

Do you think that this would help decrease our common mode noise problem?